# Performance Evaluation of 6 Transistor **D-Flip Flop based Shift Registers using GDI** Technique

## M.Arunlakshman<sup>1</sup>, T.Dineshkumar<sup>2</sup>, N.Mathan<sup>3</sup>

M.Tech VLSI, Sathyabama University, Chennai, India<sup>1,2</sup>

Assistant Professor ECE, Sathyabama University, Chennai, India<sup>3</sup>

Abstract: Power dissipation is an important parameter in the design of VLSI circuits, and the clock network is responsible for a substantial part of it (up to 50%). Low Power digital CMOS becomes more and more interesting, due to the general advances in process technology and due to new low power applications. As technology advances push for smaller devices and faster operations, power consumption and become severe problems when designing high-speed ICs. These challenging concerns are mainly due to the excessive switching activity in the chip that keeps increasing proportionally to the frequency augment and the number of transistors. In this paper a new 6 transistor D-Flip-Flop based on GDI technique is designed and Shift Registers including Serial in Serial out (SISO), Serial in Parallel out (SIPO), Parallel in Serial Out (PISO), Parallel in Parallel Out (PIPO) are designed based on this newly designed D-Flip-Flop and layouts are also designed using Microwind.

Keywords: Flip-Flop, Shift Registers, GDI technique, Power, Layout.

#### **INTRODUCTION** T.

It has been shown that a significant portion (30-60%) of sequential circuit depends on the order in which the inputs the total power consumption is dissipated in the clock are changed. Sequential circuits can be used as memory distribution network and flip-flops that constitute ubiquitous elements for digital CMOS ICs design [10]. This power is dissipated in form of heat and radiation which complicate further the design of the circuit. Since the leakage current augments with temperature, the inefficient package cooling technologies used today contribute to drastically boost the power dissipation. The upcoming sections explains about the sequential circuits and the concept of GDI technique

#### SEQUENTIAL CIRCUITS П.

Flip-Flop is an electronic circuit that stores a logical state of one or more data input signals in response to a clock pulse. Flip-flops are often used in computational circuits to operate in selected sequences during recurring clock intervals to receive and maintain data for a limited time period sufficient for other circuits within a system to further process data.

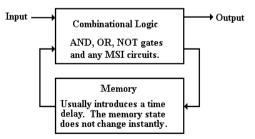

Fig. 1. Representation of Sequential Circuit

Sequential circuits have memory and combinational circuits do not. All sequential circuits contain combinational logic in addition to the memory elements. Sequential circuits are those with memory, also called "feedback". In this, they differ from combinational circuits, which have no memory. The stable output of a Copyright to IJARCCE

elements; binary values can be stored in them.

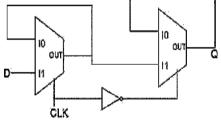

#### A. MUX based D-Flip-Flop

The flip-flop used in this paper is the double edge triggered flip-flop. The principle incorporated in the flip flop is that during the rising edge of the clock, the input value gets delayed with reference to the clock signal fed.

Fig. 2. MUX Based D-Flip-Flop

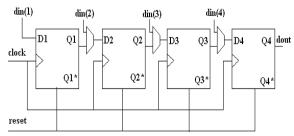

B. Serial in Serial out Shift Register

The serial in/serial out shift register accepts data serially that is, one bit at a time on a single line. It produces the stored information on its output also in serial form.

Fig. 3. Serial in Serial out Shift Register

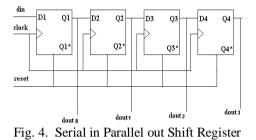

#### C. Serial in Parallel out Shift Register

This configuration allows conversion from serial to parallel format. Data is input serially, as described in the

SISO section above. Once the data has been input, it may **III.** be either read off at each output simultaneously, or it can be shifted out and replaced. Serial in parallel out diagram only is shown in fig.4 For this kind of register, data bits are oper entered serially in the same manner as discussed in the last better section. The difference is the way in which the data bits as the are taken out of the register.

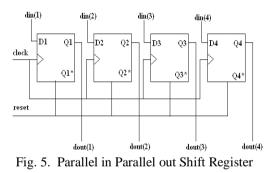

## D. Parallel in Parallel out Shift Register

For parallel in parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits. The following circuit is a four-bit parallel in - parallel out shift register constructed by d flip-flops and shown in fig 5. Both the inputs as well as the outputs performs the parallel operation. A global clock is given to activate all the flip flops connected as shown below. The D's are the parallel inputs and the Q's are the parallel outputs. Once the register is clocked, all the data at the d inputs appear at the corresponding q outputs simultaneously.

#### D. Parallel in Serial out Shift Register

This configuration has the data input on lines d1 through d4 in parallel format. To write the data to the register, the write/shift control line must be held low. To shift the data, the w/s control line is brought high and the registers are clocked. The arrangement now acts as a PISO shift register, with d1 as the data input. However, as long as the number of clock cycles is not more than the length of the data-string, the data output, q, will be the parallel data read off in order as shown in Fig.6.

Fig. 6. Parallel in Serial out Shift Register

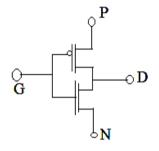

### GROUND DIFFUSION INPUT TECHNIQUE

The GDI technique is of more important because it uses only couple of transistors to construct a design. As the operation involves only two transistors, it could show better results in terms of Power Dissipation, Speed as well as the area occupied. This technique is most predominant for designing circuits in MOSFET technology. A basic GDI cell contains four terminals - G node (the common gate input of the nMOS (Negative channel Metal-Oxide Semiconductor) and pMOS (Positive channel Metal-Oxide Semiconductor) transistors), P node (the outer diffusion node of the pMOS transistor), N node (the outer diffusion node of the nMOS transistor), D node (the common diffusion of both transistors). P. N and D may be used as either input or output nodes, depending on the circuit structure shown in Fig.7. Multiple-input gates can be implemented by combining several GDI cells .GDI enables simpler gates, lower transistor count, and lower power consumption in many implementations. This technique allows reducing power consumption, propagation delay, and area of digital circuits while maintaining low complexity of logic design. The overall area and complexity of the circuit is minimized using GDI technique. Most of the functions which are complex (6-12 transistors) in CMOS, are very simple (only 2 transistors per function) in GDI design method.

Fig. 7. Symbol of GDI Cell

- IV. PROPOSED D-FLIP-FLOP AND SHIFT REGISTERS USING GDI TECHNIQUE

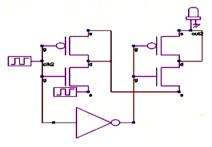

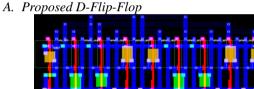

- A. Proposed 6 transistor D-Flip-Flop

Fig. 8. Proposed 6 transistor D-Flip-Flop

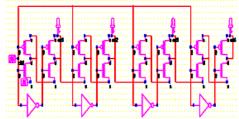

B. Proposed Serial in Serial out Shift Register

www.ijarcce.com

Fig. 9. Proposed Serial in Serial out Shift Register

5859

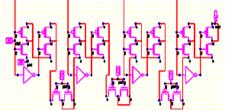

C. Proposed Serial in Parallel out Shift Register

Fig 10. Proposed Serial in Parallel out Shift Register

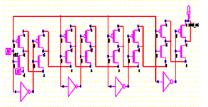

D. Proposed Parallel in Serial out Shift Register

Fig. 11. Proposed Parallel in Serial out Shift Register

E. Proposed Parallel in Parallel out Shift Register

Fig. 11. Proposed Parallel in Parallel out Shift Register

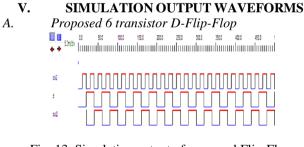

Fig. 13. Simulation output of proposed Flip-Flop

B. Proposed Serial in Serial out Shift Register

Fig. 14. Simulation output of proposed SISO

C. Proposed Serial In Parallel Out Shift Register

Fig. 15. Simulation output of proposed SIPO  $_{\mbox{Copyright to JJARCCE}}$

D. Proposed Parallel in Serial Out Shift Register

Fig. 16. Simulation output of proposed PISO

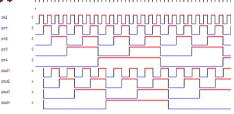

E. Proposed Parallel In Parallel Out Shift Register

Fig. 17. Simulation output of proposed PIPO

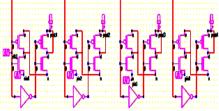

VI. LAYOUT OF FLIP-FLIP-FLOP AND SHIFT REGISTER

Fig. 18. Layout of proposed D-Flip-Flop

B. Proposed Serial in Serial out Shift Register

Fig. 19. Layout of proposed SISO

C. Proposed Serial in Serial out Shift Register

Fig. 20. Layout of proposed SIPO D. Proposed Parallel in Parallel out Shift Register

Fig. 21. Layout of proposed PISO

www.ijarcce.com

F. Proposed Parallel in Parallel out Shift Register

| B. 1777 B 8 777 B |                                   |

|-------------------|-----------------------------------|

|                   |                                   |

|                   |                                   |

|                   | ning and and and an in a sing and |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

|                   |                                   |

| 1998.<br>1992     |                                   |

|                   |                                   |

Fig. 22. Layout of proposed PIPO

#### TABLE I. POWER ANALYSIS

| Design                                     | Power (mW) |

|--------------------------------------------|------------|

| D-Flip-Flop                                | 0.002      |

| Serial In Serial Out Shift<br>Register     | 0.021      |

| Serial In Parallel Out Shift<br>Register   | 0.021      |

| Parallel In Serial Out Shift<br>Register   | 0.021      |

| Parallel In Parallel Out<br>Shift Register | 0.020      |

#### VII. CONCLUSION

Thus the D-Flip-Flop with 6 Transistors using the GDI technique is designed and shift Registers are also designed with the above descripted 6 Transistor D-Flip-Flop. It predominantly consumes very less Power compared with the conventional Flip Flop designs. The transistor count is also minimized and results in occupying of very low area. The design can also perform faster. The high end digital circuits designed with these Flip-Flop and Shift Registers will definitely show better results compared to normal designs.

#### REFERENCES

- N.Vishnu vardhan reddy, c. Leela mohan, m. Srilakshmi" gdi based subthreshold low power d- flipflop" internaional journal of vlsi and embedded systems-ijves, vol 04, article 06112; pp.502-506.

- [2] Morgenstein, A. Fish, I. Wagner, —An Efficient Implementation of D Flip-Flop Using the GDI Technique, ISCAS'04, pp. 673-676, May2004.

- [3] Morgenshtein, A. Fish, I.A. Wagner, —Gate-Diffusion Input (GDI) –Power Efficient Method for Digital Combinatorial Circuits, IEEE Trans. VLSI, vol. 10, no. 5, pp. 566-581, October 2002.

- [4] Arcady Morgenshteid, Alexander Fish2 and Israel A.Wagner3Gatediffusion input (GDI) –a novel power efficient method for digital circuits: A design methodology 0-7803-6741-3~901/\$10.000 2001 IEEE.

- [5] Mathan.N, Ravi.T and Logashanmugam.E, "Design And Analysis Of Low Power Single Edge Triggered D Flip Flop Based Shift Registers", International Journal of Emerging Technology and Advanced Engineering, Volume 3,Issue 2,Feb 2013,pp. 279-283.

- [6] Nilesh P. Bobade ,"Design and Performance of CMOS Circuits in microwind". IJCA, Jan'2012, wardha. M.S., India.

- [7] M. H. Cheng, and Z.W. Wu, "Low-power low-voltage reference using peaking current mirror circuit," ELECTRONICS LETTERS, Vol. 41, No. 10, May 12, 2005.

- [8] Mathan.N, Ravi.T and Kannan.V, "Low Power Single Edge Triggered D Flip Flop based shift registers using 32nm Technology", International Journal of Technology, Volume 2, Issue 2, Feb 2013,pp. 1-5.

- [9] Chandrakasan A.P. Sheng S. Brodersen R.W.: "Low-power CMOS digital design", IEEE Journal of Solid-State Circuits, Volume 27, Issue4, April 1992 Page(s):473 – 484.

- [10] Fabian Klass, "Semi-Dynamic Flip-Flops with Embedded Logic" IEEE Symposium on VLSI Circuits, 1998. Digest of Technical Papers, 1998 pages 108 - 109

- [11] Imran Ahmed Khan, Dr. Mirza Tariq Beg Novel Low Power and Low Transistor Count Flip-Flop Design with High Performance journal of innovative systems design and engineering vol 3, No- 11, pages 50-60.

- [12] Ravi.T, Mathan.N and Kannan.V, "Design and Analysis of Low Power Single Edge Triggered D Flip Flop", International Journal of Advanced Research in Computer Science and Electronics Engineering, Volume 2,Issue 2,Feb 2013,pp. 172-175.

- [13] Ahmed Sayed and Hussain Al-Asaad." A New low power high performance flip-flop", IEEE International Midwest Symposium on Circuits and Systems, 2006. MWSCAS '06 pages: 723 - 727.

- [14] http://www.allaboutcircuits.com

- [15] http://www.ptm.asu.edu

- [16] http://vides.nanotcad.com/vides/

- [17] http://en.wikipedia.org/wiki/Fieldeffect\_transistor

- [18] http://en.wikipedia.org/wiki/Flipflop\_(electronics)

- [19] http://en.wikipedia.org/wiki/low power

- [20] http://en.wikipedia.org/wiki/Moore's\_law

- [21] http://en.wikipedia.org/wiki/MOSFET

- [22] http://en.wikipedia.org/wiki/Transistor

# BIOGRAPHIES

**M.Arunlakshman** was born in Nagercoil, TamilNadu India on 01/11/1989. He completed his bachelor's degree in Electronics and Communication Engineering from Anna University,

Chennai, Tamilnadu, India. He is currently pursuing his M.Tech in VLSI DESIGN at Sathyabama University, Chennai, Tamilnadu, India. Previously after completing bachelor's degree he worked as a Technical Support Executive for a period of one year in HCL Technologies. Greams Road, Chennai-600006, TamilNadu, India. He is having publications in national/international conferences and journals. His interested areas are Low Power VLSI, Digital Electronics.

**T.Dinesh kumar** was born in thuraiyur, trichy district, tamilnadu state, india in 1989. He received the B.E in electronics and communication engineering from SRR engineering college in 20110. From 2011 to

2012, he worked as maintenance engineer in sunstar scientific instruments private limited company. Now, he is studying M.tech vlsi design in Sathyabama University. His research interest include low power vlsi ,design, testing and verification of vlsi systems.

**Mathan.N** was born in Nagercoil, Tamilnadu, India in 1989. He received his Bachelor Degree in Electronics and Communication Engineering from Anna University, Chennai in the year 2010. Master

Degree in VLSI Design from Sathyabama University, Chennai in the year 2013. He is working as Assistant Professor in Department of ECE in Sathyabama University. His interested areas are Nano Electronics, VLSI Design, Low Power VLSI Design, Testing of VLSI circuits and Advanced Digital System Design. He has Research publications in National / International Journals /Conferences.