# Low power wallace and dadda multiplier based on CLRCL full adder

R.Naveen<sup>1</sup>, K.Thanushkodi<sup>2</sup>, C.Saranya<sup>3</sup>

Assistant Professor, ECE, Info Institute of Engineering, Coimbatore, India<sup>1,3</sup>

Director, Akshaya College of Engineering and Technology, Coimbatore, India<sup>2</sup>

Abstract: Multiplication is one of the most critical arithmetic operation, which is extensively used in many VLSI systems such as application specific based digital signal processor architectures and microprocessor. Multipliers are the major source of power dissipation in the VLSI systems. By reducing the power consumption of the multipliers the power consumption of the VLSI system can be reduced. This paper presents the CLRCL full adder based 4\*4 Wallace and Dadda multipliers. The CLRCL full adder has only ten transistors which is less in number when compared with conventional full adders which is used to design these multipliers. Designing Wallace and Dadda multiplier by using CLRCL full adder will reduce the transistor count and power consumption. The proposed design is simulated using 0.12µm.

Keywords: Full adder, multiplier, Power consumption, Wallace multiplier, Dadda multiplier

## I. INTRODUCTION

The multipliers play a major role in digital signal processing applications and microprocessors. Currently the need for low power multiplier has been increased due to immense increase in portable devices. However, with the advance of VLSI technology, the computation speed can be improved at a constant pace. Instead, power consumption has been a more and more prominent design factor under the prevailing of battery operated mobile devices. Power consumption if a VLSI system increased when the chip density is increased [1].So the major consideration while designing multipliers is power consumption.

C.S.Wallace suggested a fast multiplier during 1964 with combination of half adders and full adders[2] Later the Wallace multiplier with full adder design showed rapid development in power consumption [3]. Luigi Dadda suggested a parallel multiplier during 1965 with half adder and full adder. Then Dadda multiplier with full adder showed rapid development in power consumption[4].For both the multipliers full adder is the basic unit .So the power consumption of the full adder will have an impact on these multipliers. Here Complementary and Level Restoring Carry Logic adder(CLRCL) full adder is used to design 4\*4 Wallace and Dadda multiplier to its less transistor count and low power consumption [5]. The simulation results shows rapid development in power consumption of 4\*4 Wallace and Dadda multipliers when compared with conventional full adders like 28T,16T,14T based Wallace and Dadda multipliers.

### II. EXISTING WORK

An Dadda and Wallace multiplier are efficient hardware implementation of digital circuit that multiplies two integers. Initially a 4\*4 Wallace and Dadda multipliers were designed using conventional full adder .This full adder had 28 transistors [6]. The schematic diagram of 28T full adder is shown in Fig. 1.

Copyright to IJARCCE

Fig. 1Schematic diagram of 28T Full Adder

Then 4\*4 Wallace and Dadda multiplier are designed by using 28T full adder[7] as shown in Fig. 2and Fig. 3.The Wallace multiplier design has 280 transistors and the 4\*4 Dadda multiplier has 336 transistors.

Fig. 2Schematic diagram 28T Full Adder based4\*4Wallace Tree Multiplier

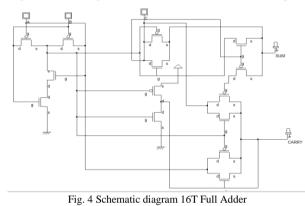

Later a 16T full adder is proposed. This full adder has 16 transistors [8] which is less in number when compared with 28T full adder as shown in Fig. 4.

International Journal of Advanced Research in Computer and Communication Engineering Vol. 3. Issue 12. December 2014

Fig. 3Schematic diagram 28T Full Adder based4\*4Dadda Multiplier

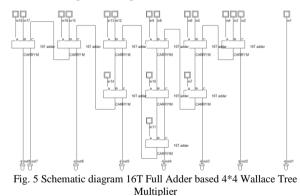

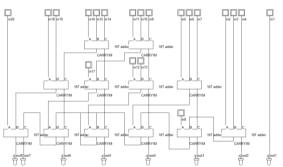

Then 4\*4 Wallace and Dadda multiplier were design using 16T full adder[7]. From these design the transistor count of Wallace Tree multiplier is 160 and Dadda multiplier is 192 as shown in Fig.5 and Fig. 6.

Fig. 6Schematic diagram 16T Full Adder based 4\*4 Dadda Multiplier

Many researches had been done in terms of transistor count to reduce the power consumption of multipliers. Then a 14T full adder is proposed which has only 14 transistors [9] as shown in Fig. 7.

Fig. 7Schematic diagram 14T Full Adder

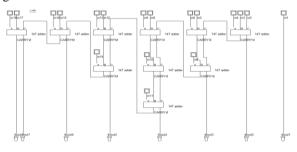

A 4\*4 Wallace Tree multiplier and Dadda multiplier were designed using 14T full adder[7] as shown in Fig. 8 and Fig. 9

Fig. 8 Schematic diagram 14T Full Adder based 4\*4 Wallace Tree Multiplier

Fig. 9 Schematic diagram 14T Full Adder based 4\*4 Dadda Multiplier

From the 14T full adder based Wallace and Dadda multipliers has 140 and 168 transistors respectively which is less in number when compared with 28T,16T full adder multipliers.

#### **III.PROPOSED WORK**

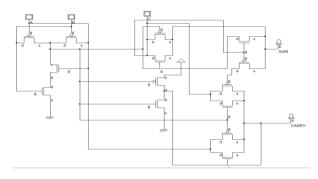

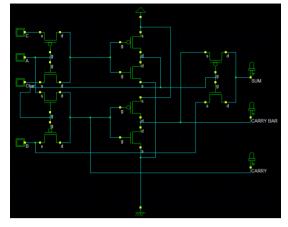

The proposed work presents the design of low power 4\*4 Wallace and Dadda multipliers based on CLRCL full adder. Though different multipliers exists [10] here Wallace and Dadda multipliers is chosen due to its high performance and speed.CLRCL full adder has less number of transistors and power consumption when compared with existing adders [5] as shown in Fig.10.

Copyright to IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering Vol. 3, Issue 12, December 2014

Fig. 10 Schematic diagram of CLRCL Full Adder

This full adderhas two major advantages when compared with existing adders.First one is it act as level restoring circuit to contest the output threshold voltage loss. Second one is the inverter in this design serves as a buffer along the carry chain to speed up the carry propagation. The ultimate intention of this full adder is that the carry signal must not suffer from distortion as it is propagated. Here a 4\*4 Wallace multiplier is designed with the help of CLRCL full adder as shown in Fig. 11

Fig. 11 Schematic diagram CLRCL Full Adder based 4\*4 Wallace Multiplier.

The proposed design has 10 CLRCL blocks with 100 transistors and power consumption of  $0.591\mu$ W.A 4\*4 Dadda multipliers is designed using CLRCL full adder as shown in Fig.12.This design has 210 transistors and  $0.437\mu$ W power consumption.

Fig. 12Schematic diagram CLRCL Full Adder based 4\*4 Dadda Multiplier Copyright to IJARCCE

#### IV. RESULTS AND COMPARISON

# A. Results

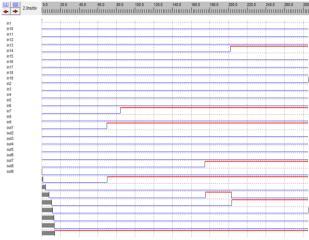

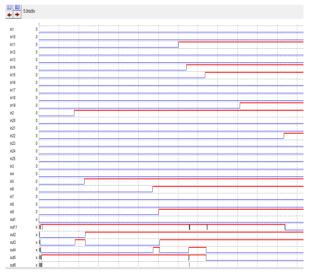

The proposed 4\*4 Wallace multiplier and Dadda multipliers are simulated using  $0.12\mu$ m technology in microwind 2 tool. From the simulation results the Wallace and Dadda multiplier consumes less power when compared with conventional full adders based Wallace and Dadda multiplier. The simulated waveforms of these multipliers are shown in Fig. 13 and Fig. 14.Digital signal processing applications become more efficient by using these multipliers.

Fig. 13Waveform of CLRCL Full Adder based 4\*4 Wallace multiplier.

Fig. 14 Waveform of CLRCL Full Adder based 4\*4 Dadda Multiplier.

#### B. Comparison

A comparative analysis is made between CLRCL based Wallace multiplier and conventional adder based Wallace tree multiplier is shown in Table 1.And Table 2 shows the comparative analysis between CLRCL based Dadda multiplier and Conventional adder based Multiplier.Table 1 and Table 2 shows that CLRCL based Wallace and Dadda multipliers were better in terms of transistorcount and power consumption when compared with 28T, 16T and 14T fulladder based multipliers.

DOI 10.17148/IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering Vol. 3, Issue 12, December 2014

TABLE I

COMPARATIVE ANALYSIS OF WALLACE MULTIPLIER

| Wallace<br>multiplier | Transistor<br>count | Power<br>consumption |

|-----------------------|---------------------|----------------------|

| 28T based             | 280                 | 8.58w                |

| 14T based             | 140                 | 8.60w                |

| 16T based             | 160                 | 8.50w                |

| CLRCL based           | 100                 | 0.591µw              |

TABLE II

COMPARATIVE ANALYSIS OF DADDA MULTIPLIER

| Dadda<br>multiplier | Transistor<br>count | Power<br>consumption |

|---------------------|---------------------|----------------------|

| 28T based           | 336                 | 1.378uW              |

| 14T based           | 168                 | 1.091uW              |

| 16T based           | 192                 | 0.891uW              |

| CLRCL based         | 120                 | 0.827uW              |

#### V. CONCLUSION

In this paper, the power consumption and transistor count of 4\*4 Wallace tree multiplier and Dadda multiplier were realized using CLRCL full adder. For comparative analysis these multipliers were realized with 28T, 16T and14T full adders. In all the Wallace and Dadda multiplier configuration investigated, the CLRCL full adder based Wallace and Dadda multiplier exhibited better result interms of transistor count and power consumption. These multipliers based on CLRCL full adders are worth enough to make the performance of digital signal processor more efficient.

#### References

- [1] John P.Uymera, "Introduction to VLSI Circuits and Systems"

- [2] C.S.Wallace."A Suggestion fora fast multiplier",IEEE Trans.Electron.Vol EC-13,pp 14-17,Feb 1964.

- [3] R.Naveen,K.Thanushkodi and C.Saranya,"Leakage power reduction in Wallace tree multiplier using current comparison domino logic", JATIT, Volume 55, No 1, 2013.

- [4] Kenneth Steiglitz and Peter R Capello,"A VLSI layout for a pipelind Dadda multiplier", ACM transaction on computer systems Vol-1,no-2,pp 157-174,pg.983.

- [5] K.Nehru, A.Shanmugam, S.Vadivelu," CLRCL based low power architectures", IJVES, Vol-3, no-1, 2012.

- [6] Y.SunilGavaskar Reddy and V.V.G.S. Rajendra Prasad, "Power Comparison of CMOS and Adiabatic Full Adder Circuits," International Journal of VLSI Design and Communication Systems, Vol.2, No.3, September 2011.

- [7] R.Naveen,K.Thanushkodi,Preethi,C.Saranya,"Asurevy of low power Wallace and Dadda multiplier using different logic full adders",IJRET, Vol-3,no-11,2014.

- [8] Hajar Zare Bahramabadi,Hamidreza Dalili Oskouei,Asghar Ebrahimi,"Design of Low power full adders for arithmetic applications "International Journal Of Emerging Science and Engineering,Vol.1,2013.

- [9] SubodhWariya, Rajendra Kumar Nagaria and Sudarshan Tiwari, "Comparative Performance Analysis of XOR-XNOR Function based High-Speed CMOS Full International Journal of VLSI Design and Communication Systems, Vol.3, No.2, April 2012.

- [10] Shiwani Singh, Tripti Sharma, K.G.Sharma and Prof.B.P.Singh, "Low Power 1-Bit 9T Full Adder Cell using XNOR Logic," Proc. of the Intl. Conf. On Advances in Computer Science and Electronics Engineering,2012.