International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 8, August 2015

# Offline PLC Failure Detection Method: A Case Study

Mr Atul B. Vitekar<sup>1</sup>, Prof Dr M. S. Nagmode<sup>2</sup>, Alok Pawar<sup>3</sup>

PG Student, Department of Electronics & Telecommunication, M.I.T College of Engineering, Pune, India<sup>1</sup>

Professor, Department of Electronics & Telecommunication, M.I.T College of Engineering, Pune, India<sup>2</sup>

Research Associate, Regional Laboratory for Applied Research and Development, Pune, India<sup>3</sup>

Abstract: Today's automotive industry are demanding for flexible and capable of producing multiple vehicles in multiple variations on a single line. Such automation also requires guaranteed output with safety critical consideration. With the increase in flexible manufacturing comes more parts, more variation and programs, and more interfaces to robots and other devices. To maintain continual operations without reprogramming all of the equipment or reconfiguring entire control architecture to ensure output and productivity remain high. This paper discusses about the implementing offline failure detecting method of any Programmable Logic Controllers (PLCs) and the test result.

Keywords: Ladder Diagram, Logic Analyser, PLC, State Machine, VHDL.

## I. INTRODUCTION

automation PLCs that exist in complex automation consists of a regular array of logic, an architecture that solution e.g. Automation industry, semiconductor industry, lends itself to very complex designs. food and medical industry, etc. In the automobile industry in each production line there are various parts that will be assembled in the car considering various parameters like detecting welds in the given job, cutting position, angle and position of automobile chasses, nuts positions, etc. Performing all these activities the production line should be flexible so that if there is any change in the parts we should be able to perform it. So while increasing in the production there was some random failure problem in the PLCs. The PLC failure reasons were unknown, and as the system gets failed there is a high risk for the industry, their workers and financial loss. To detect the fault in the system we have developed an offline testing unit which consists of an emulator of various inputs and those inputs are feed to the PLC. The emulator provides these inputs to PLC at various speeds and there parameters are monitored using a logic analyzer.

## **II.SIGNIFICANCE OF OFFLINE PLC TEST UNIT**

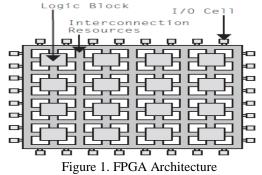

A PLC is a microprocessor-based controller with multiple inputs and outputs. It uses a programmable memory to store instructions and carry out functions to control machines and processes [1]. It is programmed to help of ladder diagram which has many rungs containing electromechanical inputs and outputs. It provides stability, accuracy and human safety, so it acts as the central controlling unit in most of the automation industry. It decides the controlling action that has to be executed while running the complex system. The inputs and outputs of the PLC are providing the protection to isolate the microprocessor from getting it damage from electrical fluctuation. Field Programmable Gate Arrays (FPGAs) are integrated circuits that enable designers to program customized digital logic in the field. FPGAs are given this name because they are structured very much like a gate

Today, many of the industries uses devices to control and array ASIC. As shown in fig. 1, like an ASIC, the FPGA

FPGAs are pre- fabricated silicon devices that can be electrically programmed to become almost any kind of digital circuit or system. They provide a number of convincing merits over fixed-function Application Specific Integrated Circuit (ASIC) technologies such as standard cells. The important thing to note about the FPGA architecture is its regular, ASIC-like structure. This regular structure makes FPGAs useful for all kinds of logic designs. Many newer FPGA architectures are incorporating complex devices inside their FPGAs. Reprogrammable FPGAs are capable of dynamically changing their logic and interconnect structure to adapt to changing system requirements. This offers a new computing paradigm, which blurs the traditional lines between hardware and software. The automation in the automobile industry is present in many ways. The production line is having various functionality in the task like assembly of various parts, positioning and inclination on the part, etc. While performing all these activities at the same time the production rate also have to be very high because of the market needs. To maintain the good production rate the field of automation plays a very important role. As the production rate is increased the

# International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 8, August 2015

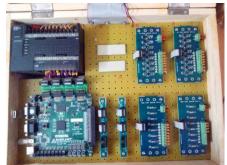

speed of operation and their controlling action also sequences. Figure 4.shows the actual hardware setup. increases. This impacts on the speed of the operation of controlling unit, but because of the increased speed the performance also changes. In our application the controlling action of PLC didn't give the desired performance. The performance variation was very random. This was causing an increase in the risk for the industry as well as their workers. This was a growing problem for that industry, as they don't want to take more risk toward their worker. While studying there system we have developed this offline testing unit that was able to find the exact problems. This unit helped them to find the problem and later the errors was removed, which ultimately reduce the risks.

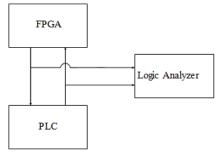

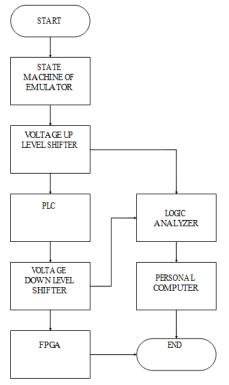

Figure 2. System Block Diagram

# **III. SYSTEM HARDWARE DESIGN**

Figure 2 shows the system block diagram in which it is depicting the important blocks of the system as FPGA, Logic Analyser and PLC. The FPGA is used as an emulator which generate different test inputs for the offline PLC. PLC will generate the output as per the emulated input signals. The operation of PLC is being monitored on logic analyser. The speed of the emulated signal can be easily controlled by the user using FPGA with the help of slider switches present on it.

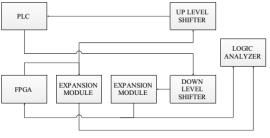

Figure 3. System Architecture

Figure 3 shows the architecture diagram of the system. The input and output signals generated by the FPGA are TTL level and for PLC it is 24V. As these two voltage logics are not compatible with each other, we need to introduce up and down the voltage level sifter. The FPGA is having all possible test sequences and it is generated at a specific production rate. This production rate is being varied variable slider switch combinations.

Now these input sequences are fed to the PLC to generate respective outputs according to the ladder diagram. These outputs are observed on logic analyser as well as it is fed t FPGA again to display on LEDs present on the FPGA board so that the user can see the changes in the output

Figure 4. Hardware Setup

# **IV. SYSTEM SOFTWARE DESIGN**

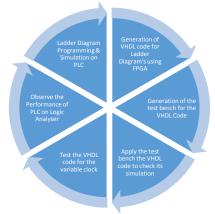

Figure 5 show the implemented methodology for the offline PLC test unit. First, we have studied PLC ladder diagram programming, its implementation and simulation on the PLC.

Figure 5. Methodology

Figure 6. Flow Chart

#### International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 8, August 2015

We have implemented ladder diagram for a small application and its performance analysis on it. Then we have created the VHDL code for the inputs of a PLC at variable operating speed. These emulated signals were generated with the help of the FPGA. Before actually feeding these signals to PLC we have actually simulated these programs using VHDL test bench on ISim simulator. After providing these input sequences to PLC we have monitored and analyse the output sequences using a logic analyser Figure 6 shows the flowchart of the software program developed to generate the test sequences at variable clock speed measured in Hz.

## V. RESULT & ANALYSIS

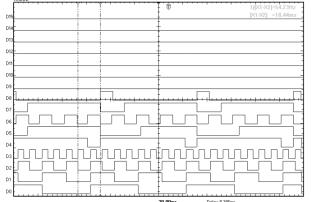

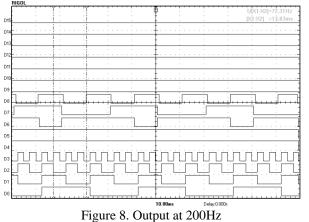

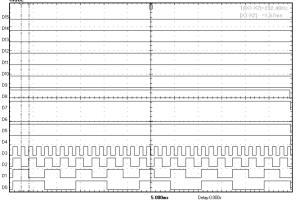

Figure 7, 8 and 9 shows the output observed on logic analyzer. Where X axis is the Time in milliseconds. Y axis has various digital channel numbers. D0, D1 and D2 are emulated test pattern for PLC generated by the FPGA. D3 is variable clock set by the user using slider switch. D4-D8 are variable output sequences generated by the PLC.

From the figure 7 and 8 we have observed that PLC has not generated the output at the same instant of input applied due to which there are variable delays at variable output clock speed which also affects the speed of operation of production line.

From figure 9 we can see that, at 300 Hz or more than that of the clock PLC fails to generate the output though FPGA generates input sequences continuously and there is no output change by PLC i.e. D4-D8 are freeze. This causes the control failure of the production line.

Figure 7. Output at 100 Hz

Figure 9. Output at 300 Hz

With the help of the offline PLC test unit we have detected that after a specific production rate the PLC was not able to control the different devices. Due to the delays generated by the PLC in the controlling action, the production line was not efficiently performing its task. Such kind of errors can be easily analysed or monitored by our system that help plant engineer to minimize the errors generated in the actual production line.

#### VI. CONCLUSION

From this case study we can see there are certain limitations in PLC while operating at high production rate due to which random errors are generated during production and there is a high risk for industry, the workers and financial losses. These errors are generated because of the internal architecture of PLC, as it is a microprocessor or microcontroller based system the execution of rungs are done in a sequential manner and it fails to perform parallel process.

#### REFERENCES

- [1] Kevin Collins," PLC Programming for Industrial Automation ", Sixth edition, Triangle Research International, 2006.

- [2] Frank D.Petruzella", Programmable Logic Controllers", Fourth edition, McGraw-Hill Science/Engineering/Math, 2010

- [3] W.Bolton," Programmable Logic Controllers ", Second edition, Newnes, 2009

- Douglas Perry," VHDL: Programming by example", Fourth edition, [4] McGraw Hill, 2002.

- [5] Park Chang Mok, Bajimaya Sachin Man, Park Sang C., Wang Gi Nam, Hee Han, Chang Minho, Kwak Jong Geun, Kwan "Development of Virtual Simulator for Visual Validation of PLC Program", International Conference on Computational Intelligence for Modelling Control and Automation,2006 IEEE.

- Thapa Devinder, Park Chang Mok, Dangol Suraj, and Wang Gi-Nam, "III-Phase Verification and Validation of IEC Standard Programmable Logic Controller", International Conference on [6] Computational Intelligence for Modelling Control and Automation, Web Technologies and Internet Commerce, 2006 IEEE.

- Cheon S.W., Lee J.S., Won K.C.K, Kim D.H., "The Software [7] Verification arid Validation Process for a PLC-based Engineered Safety Features-Component Control System in Nuclear Power Plants", The 30th Annual Conference of the IEEE IES, Busan, Korea, Nov. 2004, pp.827-831

- [8] Gourcuff Vincent, De Smet Olivier and Faure Jean-Marc, "Efficient representation for formal verification of PLC programs". Proceedings of the 8th International Workshop on Discrete Event Systems Ann Arbor, Michigan, USA, July 10-12, 2006 IEEE, pp.182-187

- Kajihara Shigeru, Ono Masahide, Houzouji Harumi, Tamishi Hajime, Takayanag Yoichi, "Development and Products of the [9] Object-Oriented Engineering Tool for the Integrated Controller based on IEC 61131-3", SICE Annual Conference in Sapporo, Hokkaido Institute of Technology, Japan, August 2004, pp. 1952-1956.