International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 9, September 2016

# High Performance Smart Routing for Network on Chip

Himani Mittal<sup>1</sup>, Dr. Yogendera Kumar<sup>2</sup>

Research Scholar, VLSI Division, School of Electrical, Electronics and Communication Engineering,

Galgotias University, Greater Noida, (UP) India<sup>1</sup>

Professor, VLSI Division, School of Electrical, Electronics and Communication Engineering, Galgotias University,

Greater Noida, (UP) India<sup>2</sup>

Abstract: With the advancement of Very-large-scale integration (VLSI) technology, research is going on to build more complex and robust computing systems in a single silicon chip. Interconnection requirements increase with a rapid pace with the increase of the number of components that appear on the chip thereby posing a limitation on overall on performance. Keeping this in mind we try to propose a Network on chip. The idea of a Network-on-Chip (NoC) borrows networking theory from the computer networking domain and considers each intellectual property (IP) core as a single node. In each node, a high-speed router connects with other routers of neighboring nodes. In a nutshell, the tradeoff between performance, area, and power is significant while designing routers of Network on chip. According to literature survey, the router architecture always contains buffers on the input ports. The buffer scheme is used to store packets; these packets must wait for the output resource due to contention with other packets. These designs have been widely adopted due to their improved performance. Finally, we propose a smart routing with low power, low area and improved performance. In our design Loop Back module is designed as old one, FSM is removed ,Routing Error detection , Logic, centralized Journal of data Packet are removed as our loop back module itself does the same functionality ,Ordinary Buffers are removed , instead of FIFO is used to achieve better performance.

**Keywords:** Hamming code, Loop Back Module, FIFO, Adaptive algorithm, dynamic reconfiguration, network-on-chip (NoC), reliability, performance, area, power, latency.

#### I. INTRODUCTION

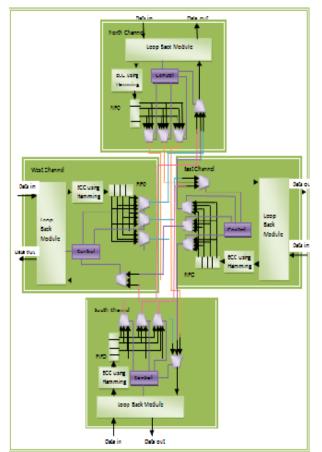

The NoC features a high level of modularity, flexibility, and throughput. Network on chip comprises routers and interconnections allowing communication between the PEs and IPs [1]. The NoC relies on data packet exchange. The path for a data packet between a source and a destination through the routers is defined by the routing algorithm [6]. Therefore, the path that a data packet is allowed to take in the network depends mainly on the adaptiveness permitted by the routing algorithm (partially or fully adaptive routing algorithm), which is applied locally in each router being crossed and to each data packet To achieve a reconfigurable NoC[4], an efficient dynamic routing algorithm is required for the data packets. The goal is to preserve flexibility and reliability while providing high NoC performance in terms of throughput [3]. Fig. 1 illustrates a dynamic reliable NoC.[2] Fig. 1(a) So dynamic component placement and faulty nodes or regions are the main reasons why fault-tolerant or adaptive algorithms have been introduced and used in runtime dynamic NoCs [4].

Regarding adaptive or fault-tolerant routing algorithms, several solutions have been proposed [6]. Generally, these algorithms correspond to a modified XY [1] routing algorithm that allows faulty or unavailable regions to be bypassed.

The remaining of this paper is organized as follows.

Section II describes the literature survey,

Section III Presents approach and motivation involved [2]

Section IV. Our proposed smart RKT switch.

Section V. presents results as logical simulation results of proposed router, synthesis reports,

Section VI calculations.

Finally, in Section VII conclusion and future works are given.

#### **II. LITERATURE SURVEY**

N.O.C is the most hot topic for research in today's time, In [1] it describes about the communication between processing elements, and present NoCs designs, provide integrated solutions to challenging design problems in the communications between different IPs. After a deep survey we find different router architecture like in [2] it describes about a new network-on-chip (NoC) that handles accurate localizations of the faulty parts of the NoC. [3] Presents a new shared buffer based router architecture employing dual buffers. [4] Presents Network-on-Chip (NoC) suitable for Dynamically Reconfigurable Multiprocessors on Chip systems. This NoC is based on routers performing online error detection of routing

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

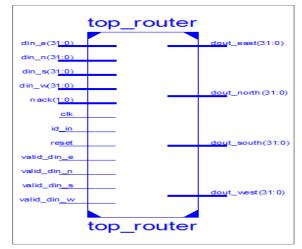

algorithm [6] and data packet errors. These routers contain modified router switch is shown in fig 1. This switch is very important part buffers [5] which are having own appropriate for 2-d mesh NoC, with four directions (north, advantages and disadvantages. Keeping all this in mind it south, east, and west) and the PES and IPS can be is required to design a router with optimum performance, [8] discuss that power, area[7], and performance of the NoC architecture are tightly integrated with the design and optimization of the link, router (buffer and crossbar), and topology.

In all the router architecture discussed so far suffered from drawbacks like more space utilized for buffers, low power but at the cost of more area. So in our work we try to get optimum performance by efficiently using buffers and by using modified error detection techniques.

#### **III. APPROACH AND MOTIVATION**

In this work, the proposed design is a new smart reliable dynamic router for NoC.

Our approach includes using FIFO for low area, low power and due to the FIFO logic used in the routing logic, B. F.I.F.O which makes router to achieve better than the existing router. As well as low overhead.

#### **IV. PROPOSED ARCHITECTURE**

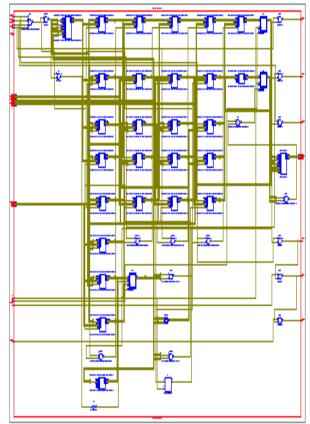

Fig. 1. Architecture of proposed router switch

The proposed architecture is modified version of router overcomeme both dead and live locks. The figure of the reconfigurable NoC, position and number of components

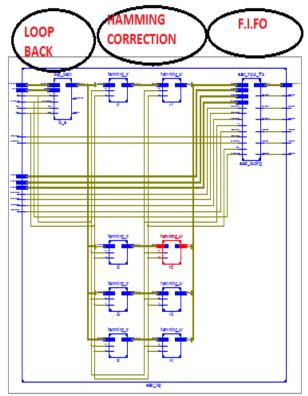

connected directly to any side of a router. There is no need for specific connection port for a PE or IP. Each port direction is composed of two unidirectional data buses (input and output ports). The proposed algorithm having no of blocks, they are loopback module, Control Logic, ECC using hamming, F.I.F.O buffer.

#### A. DIFFERENCES BETWEEN PROPOSED AND **ORIGINAL** [2] ARCHITECTURE

In the proposed work Loop Back module is designed as old one, FSM is removed and Routing Error detection, Logic, centralized Journal of data Packet is removed, as our loop back module itself does the same functionality. Buffers are also removed, instead of FIFO is used to achieve better performance.

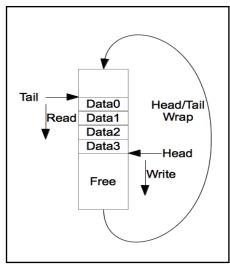

Fig.2. F.I.F.O Block Diagram

A FIFO buffer stores data on a first-in, first-out basis. The storage structure is typically an array of contiguous memory. Data is written to the "head" of the buffer and read from the "tail". When the head or tail reaches the end of the memory array, it wraps around to the beginning. If the tail runs in to the head, the buffer is empty. But if the head runs in to the tail, the implementation must define if the oldest data is discarded or the write does not complete. In the example below, data is never discarded. FIFOs are a storage mechanism which operates on a first-in, first-out basis. They are useful for managing the arrival of asynchronous data.

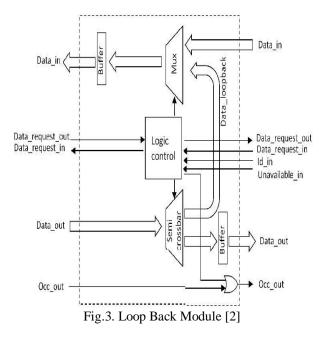

#### C .LOOPBACK MODULE

A loopback module block[2] is used for altermate path for packets by looping back through another port. This happens when neighbour router to which data is supposed switch[2] by C.KILLIANS. The proposed one will to be sent is found faulty by present router. Since it is a

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

in the network can change during the reconfiguration time. During reconfiguration, ell as faulty routers are made isolated from non faulty routers. If it is not done, data packet may get lost and never reaches its destination. To solve this problem there come loopback module which is associated with the router architecture contain output buffer. The work of loopback module is to empty the buffers of loopback module for each output port by looping back the data packet in to the input port of the router [2]. Then looped back packets are rerouted towards another output port of the router. The loopback module avoids data packet getting trapped or data packet loss. A loopback module is implemented in each of the four ports of the router. The architecture of the loopback module is depicted in Fig. 3.[2]

#### D. E.C.C USING HAMMING CODE

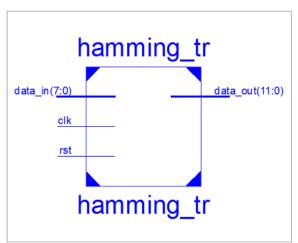

In this work we have used modified hamming code [10] to reduce area than the normal hamming code.Error in data can be easily find out and retrieved back by using the reference parity bit associated with the original data bit. This method is composed of a Transmit matrix.

The Transmit matrix is a combination of an identity matrix and a parity matrix. The input data (8-bits) is multiplied and with the identity matrix and this data bits are encoded and sent to the next router along with the parity bits. By using the parity matrix the received code word is decoded and hence the original data can be retrieved back.

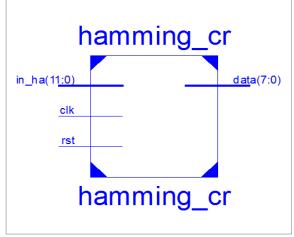

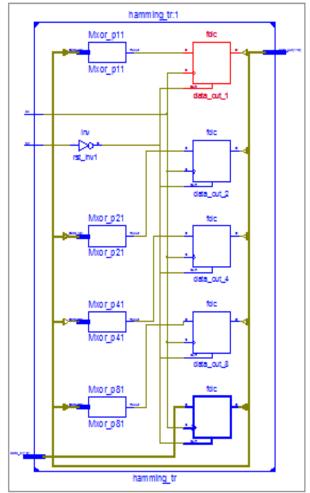

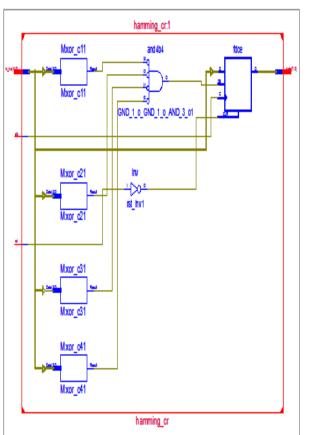

The decoder and encoder circuit structure is formed from the Transmit and Parity matrix. The encoding process is done with the help of Transmit matrix multiplied with the original data. The output of this is associated with the parity bit for the encoding reference. This method is carried out by Xor gate for each row of Parity matrix. Fig.4 and 5 show RTL view of hamming encoder and hamming decoder.

Fig.4. Hamming Encoder

FIG.5. Hamming Decoder

#### E. CONTROL LOGIC:

In addition to this physical connection infrastructure, the router also contains a logic block that implements the flow control policies (routing, arbiter, etc.) and defines the overall strategy for moving data though the NoC.

A flow control policy characterizes the packet movement along the NoC and as such it involves both global (NoClevel) and local (router-level) issues. One can ensure a deadlock-free routing, for instance, by taking specific measures in the flow control policy (by avoiding certain paths within the NoC for example). Also, the optimization of the NoC resources usage (channels, bandwidth, etc.) and the guarantees on the communication can be ensured as part of the flow control policy (for instance, by choosing a routing algorithm that minimizes the path or by implementing virtual channels to reduce congestion, etc.). The routing algorithm [6] (should avoid deadlock and livelock) is the logic that selects one output port to forward a packet that arrives at the router input. This port is selected according to the routing information available in the packet header.

According to XY routing algorithm Fig.6. That we use in paper.

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

| Algorithm Condition          | Direction Selected |

|------------------------------|--------------------|

| X destination < X previous   | NORTH              |

| X destination $>$ X previous | SOUTH              |

| Y destination < Y previous   | WEST               |

| Y destination > Y previous   | EAST               |

Fig.6. XY Routing Algorithm

#### V. RESULTS

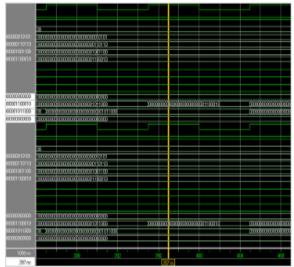

#### A. SIMULATION OF TOP ROUTER

Fig,6.. Simulation of Proposed Router

Fig.6. shows the simulations of proposed router, It is seen that all then, N, S, W, E modules send a data packet simultaneously and similarly receive the data packets simultaneously. It is also observed that all the data packets do not make any loopback and bypass as there is no fault present. Here it is showing that the data is input in four directions and after routing data is out from four directions N,S,E,W according to XY algorithm.

### B. RTL VIEW OF PROPOSED ROUTER

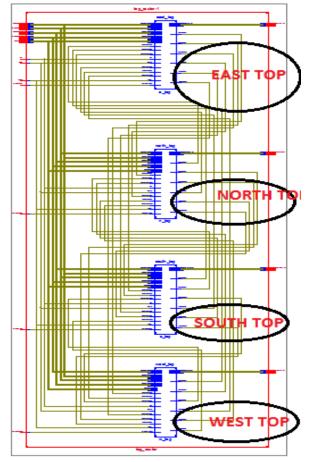

Fig .7. Top Level Architecture

Fig.8. RTL view of Top Router

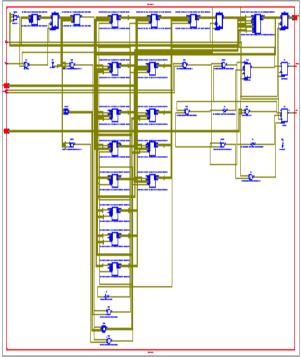

Fig.9. RTL view of EastTop Router

# International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified Vol. 5, Issue 9, September 2016

Fig.10.. RTL view of Loopback of EastTop Router

Fig.11. RTL View of Hamming Coder of East Top

Fig12.. RTL View of Hamming Decoder of East Top

Fig.13. RTL View of East Top Routing

#### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

**IJARCCE**

Vol. 5, Issue 9, September 2016

#### C. DELAY

| n Klinx-15E-CWUInknewyrol rewyrosiae-Design Swrmany)<br>Ir Fel falt Yew Poset Source Process Window Help                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                               | - 0 <b>- 1</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CORD & XGGX OF B PPXXP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                               | 00             |

| 5 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   2 100 Josep Samay 1 100 Josep Samay 1   3 100 Josep Samay 1 1 1 1   4 100 Josep Samay 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | Inning Summary<br>Speed Schder -4<br>Minimum speriody 7.10Mrss (Near<br>Minimum speriody 7.10Mrss (Near<br>Minimu optometrical peth do<br>Inning Detail)<br>All values displayed in nanoseco<br>Inning constraints (Media peth do<br>Inning constraints) Default period<br>(Lock period) 7.00Mrss (frequent<br>Inning constraints) Default period<br>Inning constraints (Media Period) / detail<br>All values of poth / detail | buffer(TF name)   Load  <br>nt_INF_JON  NUX(e_topic)/dea_J)   240  <br>mm Trepuency: 153,000000<br>fore cloot: 7,250s<br>after cloot: 7,471m<br>lays To path found<br>nds (ns)<br>d analysis for Clook 'olls' |                |

| Design Objects of<br>w 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                | Properties<br>No object is selected                                                                                                                                                                           |                |

| Name Type<br>Tweld dry Net<br>wet mitry Interce<br>-131 (50) Interce                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •<br>•                                                                                                                                                                                                                                                                                                                                                                                                                         | Tane Value                                                                                                                                                                                                    |                |

| Console Official Weinings To Shell 🗿 Find in Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sin Console - top 🛛 🖉 Vera by Calegory 🛛                                                                                                                                                                                                                                                                                                                                                                                       | lew by Name                                                                                                                                                                                                   | Ln 992 Col 4   |

Fig.14. Total Delay

#### D. FREQUENCY

Fig.15. Total Frequency

#### E. AREA UTILISED

Fig16. Area utilized of Proposed RKT switch

#### F. POWER REPORT

| File Tools Help            |                   |            |      |                 |                 |

|----------------------------|-------------------|------------|------|-----------------|-----------------|

|                            | X Name            | Power (W)  | Used | Total Available | Utilization (%) |

| liew                       | Clocks            | 0.000      | 1    |                 | -               |

| - 🌑 Report Views           | Logic             | 0.000      | 518  | 1408            | 36.8            |

| E- Summary                 | Signals           | 0.000      | 744  |                 | -               |

| Thermal Information        | IOs 🛛             | 0.000      | 73   | 108             | 67.6            |

| Voltage Source Information |                   |            |      |                 |                 |

| Settings                   | Total Quiescent P | ower 0.019 |      |                 |                 |

| ⊖- 🖉 By Type               | Total Dynamic Po  | wer 0.000  |      |                 |                 |

| - Clocks                   | Total Power       | 0.019      |      |                 |                 |

| Logic                      |                   |            |      |                 |                 |

| Signals                    |                   |            |      |                 |                 |

| IOs                        |                   |            |      |                 |                 |

| By Hierarchy               |                   |            |      |                 |                 |

| " ( <sup>a</sup> by nearny |                   |            |      |                 |                 |

Fig. 17. Total Power Delay

#### VI. CALCULATIONS

The proposed reconfigurable router is simulated and synthesized using Xilinx ISE tool. Fig.2 gives the synthesis results in terms of Slices Registers, Slices LUTs and maximal working frequency for 32 data bus size. It is seen from synthesis result of Fig. That the 32-bits Router-Switch require 330 Registers, 518 LUTs and can operate up to 142.08 MHz on the XYLINX tool. This gives a low area when we compare it with original router results [9] which states that the 32-bits original RKT-Switch requires 4340 Registers, 6542 LUTs and can operate up to 459.6

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

MHz.. Moreover, an estimation of the power consumption of 0.019 W is given through the Xilinx XPower Estimator tool if Fig.22. The results explicits that our proposed architecture shows better performance in terms of area and low power consumption. Low area is directly proportional to decrease in latency.

#### VII.CONCLUSION

Hence our modified and optimized RKT is comparatively Low Area, Low Power; and due to the FIFO logic used in the routing logic, which makes router to achieve higher performance than the existing RKT. as well as low overhead.Low area is responsible for low latency.

#### REFERENCES

- [1] L. Benini and G. De Micheli, "Network on Chips: A New SoCs Paradigm," IEEE Computer, vol. 35, no. 1, pp. 70–78, Jan. 2002.

- [2] C. Killian, C. Tanougast, F. Monteiro and A. Dandache, "Smart reliable network-on-chip", IEEE Trans. Very Large Integr. (VLSI) Syst., 2013

- [3] Tran and B. Baas, "Achieving High-Performance On-Chip Networks With Shared-Buffer Routers", TVLSI, vol. 22, no. 6, pp.1391-1403, 2014

- [4] D. Matos, C. Concatto, M. Kreutz, F. Kastensmidt, L. Carro and A. Susin, "Reconfigurable Routers for Low Power and High Performance," IEEE Transactions on Very Large Scale Integration System, pp. 2045-2057, 20.

- [5] Chung-Kai Hsu; Kun-Lin Tsai; Jing-Fu Jheng; Shanq-Jang Ruan; Chung-An Shen, "A low power detection routing method for bufferless NoC," in Quality Electronic Design (ISQED), 2013 14th International Symposium on, vol., no., pp.364-367, 4-6 March 2013.

- [6] Shubhangi D Chawade, Mahendra A Gaikwad and Rajendra M Patrikar, "Design XY Routing Algorithm for Network-On-Chip Architecture," International Journal of Computer application, Vol. - 43, No.-21, pp. 1-5, 2012.

- [7] Cesar Albenes Zeferino, Márcio Eduardo Kreutz and Altamiro Amadeu Susin, "RASOCSS: A Router Soft-Core for Networks-on-Chip," IEEE Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Vol.3, pp.198-203, Feb 2004

- [8] D. DiTomaso, R. Morris, and A. K. Kodi, "Extending the Energy Efficiency and Performance With Channel Buffers, Crossbars, and Topology Analysis for Network-on-Chips," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 11, 2013, pp. 2141-2154.

- [9] Cedric Killian, Camel Tanougast, Fabrice Monteiro, and Abbas Dandache, "A New Efficient and Reliable Dynamically Reconfigurable Network-on-Chip," Hindawi Publishing Corporation Journal of Electrical and Computer Engineering Volume 2012, Article ID 843239, 16 pages doi:10.1155/2012/843239.

- [10] Rubina Sabeer1, Karthika Manilal2," Reliable NoC Switch Design with Enhanced Error Handling Capability," International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064