# International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

# FPGA Based Digital Filter Module

Dr. Haresh Pandya<sup>1</sup>, Mr. Mahesh Rangapariya<sup>2</sup>, Mr. Kamaldeep Gosai<sup>3</sup>, Mr. Jatin Savliya<sup>4</sup>

Professor & Head, Department of Electronics, Saurashtra University, Rajakot, Gujrat, India<sup>1</sup> Ph.D. Student & Visiting Lecturer, Department of Electronics, Saurashtra University, Rajakot, Gujarat, India<sup>2</sup> Junior Lecturer, Department of Electronics, Saurashtra University, Rajakot, Gujarat, India<sup>3</sup> Visiting Lecture, Department of Electronics, Saurashtra University, Rajakot, Gujarat, India<sup>4</sup>

**Abstract:** Digital filtering algorithms are most commonly implemented using general purpose digital signal processing chips for audio applications, or special purpose digital filtering chips and application- specific integrated circuits (ASICs) for higher rates. This paper describes an approach to the implementation of digital filter algorithms based on field programmable gate arrays (FPGAs). The advantages of the FPGA approach to digital filter implementation include higher sampling rates than are available from traditional DSP chips, lower costs than an ASIC for moderate volume applications, and more flexibility than the alternate approaches. Since many current FPGA architectures are insystem programmable, the configuration of the device may be changed to implement different functionality if required. Our examples illustrate that the FPGA approach is both flexible and provides performance comparable or superior to traditional approaches.

Keyword: Digital Filter Module, VHDL (VHSIC Hardware Description Language), FPGA (Field Programmable Gate Arrays), Electronics Switch.

#### I. INTRODUCTION

lower equipment production costs than traditional analog techniques. Additionally, more and more microprocessor circuitry is being displaced with cost effective DSP techniques and products; an example of this is the emergence of DSP in cellular base stations. Components available today let DSP extend from baseband to intermediate frequencies (IFs). This makes DSP useful for tuning and signal selectivity, and frequency up and down conversion. The most common approaches to the implementation of digital filtering algorithms are general purpose digital signal processing chips for audio applications, or special purpose digital filtering chips and application-specific integrated circuits (ASICs) for higher Advantages of using digital filters rates. This paper describes an approach to the implementation of digital filter algorithms on field programmable gate arrays (FPGAs).

Recent advances in FPGA technology have enabled these devices to be applied to a variety of applications traditionally reserved for ASICs. FPGAs are well suited to data path designs, such as those encountered in digital filtering applications. The density of the new programmable devices is such that a nontrivial number of arithmetic operations such as those encountered in digital filtering may be implemented on a single device. The advantages of the FPGA approach to digital filter implementation include higher sampling rates than are 3. available from traditional DSP chips, lower costs than an ASIC for moderate volume applications, and more

Digital Signal Processing (DSP) affords greater flexibility, flexibility than the alternate approaches. In particular, higher performance (in terms of attenuation and multiple multiply-accumulate (MAC) units may be selectivity), better time and environment stability and implemented on a single FPGA, which provides comparable performance to general-purpose architectures which have a single MAC unit. Further, since many current FPGA architectures are In-system programmable, the configuration of the device may be changed to implement alternate filtering operations, such as lattice filters and gradient-based adaptive filters, or entirely different These new DSP applications result from advances in digital filtering. This Application Note will overview digital filtering by addressing concepts which can be extended to baseband processing on programmable digital signal processors.

The following list gives some of the main advantages of digital over analog filters.

- 1. A digital filter is programmable, i.e. its operation is determined by a program stored in the processor's memory. This means the digital filter can easily be changed without affecting the circuitry (hardware). An analog filter can only be changed by redesigning the filter circuit.

- Digital filters are easily designed, tested and implemented on a general-purpose computer or workstation.

- The characteristics of analog filter circuits (particularly those containing active components) are subject to drift and are dependent on temperature. Digital filters do not

# International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

- suffer from these problems, and so are extremely stable with respect both to time and temperature.

- handle low frequency signals accurately. As the speed of DSP technology continues to increase, digital filters are being applied to high frequency signals in the RF

- (radio frequency) domain, which in the past was the exclusive preserve of analog technology.

- 4. Unlike their analog counterparts, digital filters can 5. Digital filters are very much more versatile in their ability to process signals in a variety of ways; this includes the ability of some types of digital filter to adapt to changes in the characteristics of the signal.

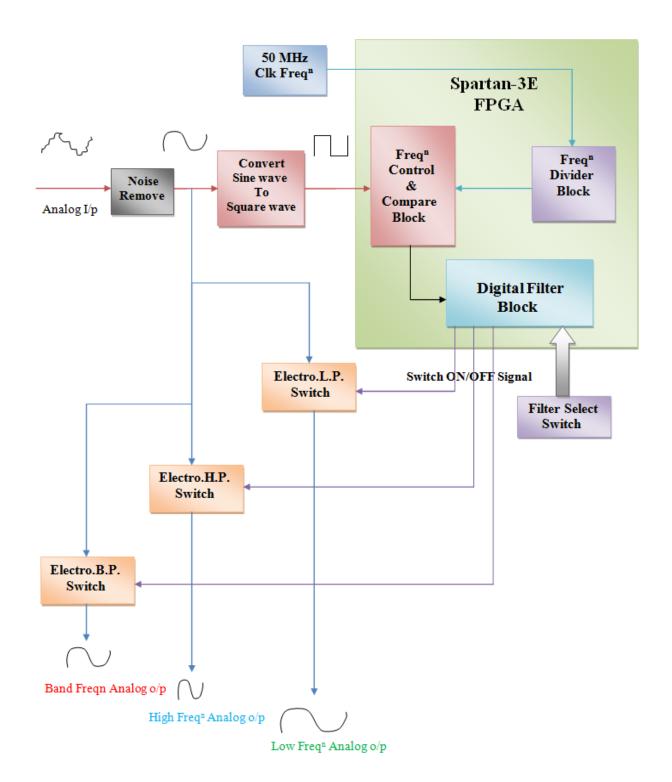

#### II. FPGA BASE DIGITAL FILTER OVERALL SYSTEM

### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

#### A. Contraction of digital filter

Shown as above figure digital filter module consist of frequency cut of Noise remove block, Sine wave to Square wave converter than or equal to block, Frequency control & Compare block, Electronics signal is active wave to square wave converter block and electronics selected high switch create outside of FPGA. Reaming block create through switch inside FPAG block using VHDL program.

Noise removes block consist of simple RC parallel network. Reactance of capacitor low for high frequency, so noise signal can't pass through RC network. Sine waves to square wave converter consist of BJT circuit. Here BJT operate in cut off and saturation region, therefore input base sine wave converts into collector square wave at the output of BJT. Another BJT and really use to making of electronics switch. Switch on/off control signal of digital filter output is high use for do on switch otherwise, switch off.

Frequency counter, frequency comparison, frequency divider and digital filter block prepare in side FPGA chip using VHDL program. FPGA chip is reconfigurable so, change functionality of all block as per over requirement. This is the main advantage of FPGA.

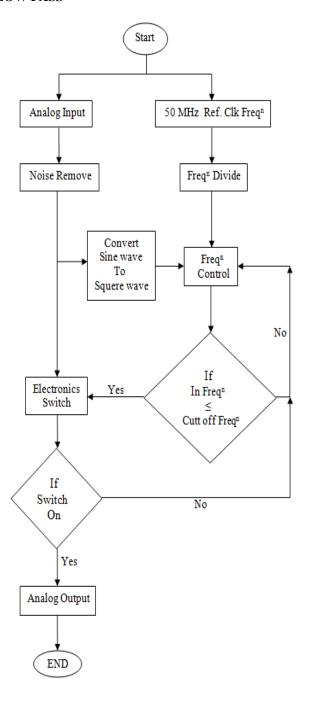

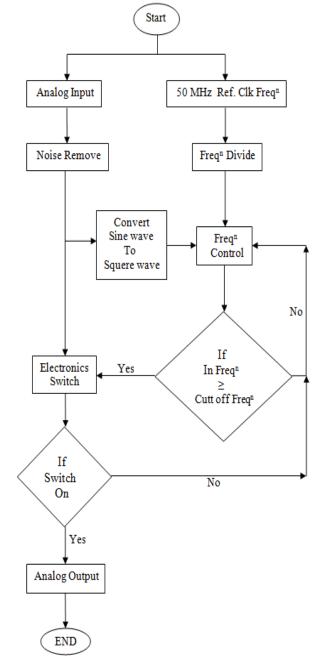

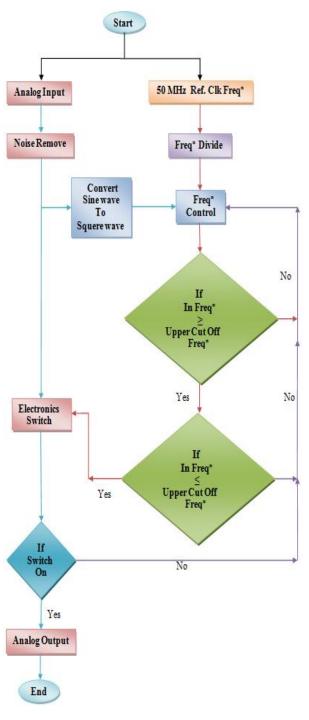

#### B. Working of digital filter

First fall analog signal with noise frequency apply to RC filter network. RC filter remove all high frequency unwanted noise signal pass only low frequency information signal. Output of RC filter is feed to two inputs, one is base of BJT and another is input of electronics switch. Electronics switch is controlled by digital output control signal. BJT operated in class c mode so, analog input convert into output pulse with same input frequency.

Converted pulse feed to input of frequency control block. This block consists of VHDL base frequency counter inside of FPGA. Frequency counter is totally controlled VHDL program, it is use to selection of cut off frequency. Parallel FPGA kit crystal produces 50MHz ref. clock frequency. This ref. frequency is applied to input of frequency divider block and they programmable by VHDL program, it is also use for selection of cut off frequency.

Frequency divider and frequency counter output feed to input of frequency compare block. Frequency compare make using VHDL program, like sequential statement object and if statement. After frequency comparisons block digital filter block divided into tree part like, low pass, high pass and band pass filter control block.

Low pass: In this section input signal feed into lower frequency cut off program. If input frequency is less than or equal to ref. clock frequency than low pass control signal is active. This low pass control signal is operate low pass electronics switch. Finally, switch is on and get selected low frequency analog signal at the output through switch.

**High pass:** In this section input signal feed into higher frequency cut off program. If input frequency is greater than or equal to ref. clock frequency than high pass control signal is active. This high pass control signal is operate high pass electronics switch. Finally, switch is on and get selected high frequency analog signal at the output through switch.

**Band pass:** In this section input signal feed into band frequency cut off program. If input frequency is greater than lower cut off and less than higher cut off of ref. clock frequency than band pass control signal is active.

#### LOW PASS

### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

This band pass control signal is operate band pass BAND PASS electronics switch. Finally, switch is on and get selected center frequency analog signal at the output through switch.

Filter selection is use for selection of filter, using this can we select low pass, high pass, band pass and all filter. Use switch for on/off filter. All filter operation is independent to each other, so freely working. Characteristic of this filter is same to ideal filter, therefore it give very sharp cut off. It means roll off rate of this filter is very high. This is not possible for analog filter.

#### HIGH PASS

# III. VHDL PROGRAMM FOR DIGITAL FILTER

- -- Company:

- -- Engineer: -- Create Date:

- 25/09/2016

- -- Design Name:

- dig Behavioral

- -- Module Name: -- Project Name:

- -- Target Devices:

- -- Tool versions:

- -- Description:

# International Journal of Advanced Research in Computer and Communication Engineering

#### ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

```

-- Dependencies:

end process;

-- Revision:

nxt<=temp;

-- Revision 0.01 - File Created

-- Additional Comments:

----low freqn senc -----

process(nxt,Clk,d1)

library IEEE:

begin

Use IEEE.STD_LOGIC_1164.ALL;

Use IEEE.STD_LOGIC_ARITH.ALL;

if(nxt='1')then

if(Clk='0')then

Use IEEE.STD_LOGIC_UNSIGNED.ALL;

if(d1'event and d1 = '0')then

---- Uncomment the following library declaration if instantiating

temp1 \le temp1 + 1;

---- Any Xilinx primitives in this code.

if(temp1=3)then

--library UNISIM;

temp1<=3; end if; end if;

--use UNISIM.VComponents.all;

else

temp1<=0; end if; end if;

entity fltr is

if(temp1=1)then

GENERIC (n: INTEGER := 7);

sc1<= '1';

Port (rst,a,bclk,ls,hs,bs: in STD_LOGIC;

else

sc1,sc2,sc3,sc4,nxt,d1,m0,m1,m2,clk:inout STD_LOGIC;

sc1<= '0';

bndpass,lps,hps,RS1,rs2,RW1,rw2,E1,e2: out STD_LOGIC;

end if;

DB1: out STD_LOGIC_VECTOR(3 DOWNTO

end process;

0));

end fltr;

---- medium freqn senc -----

process(nxt,Clk,d1)

architecture Behavioral of fltr is

begin

signal\ temp, q, q1, q2, q3, do, do1, do2, do3, dof: STD\_LOGIC := '0';

if(nxt='1')then

signal lo,ho,E,RS,RW:STD_LOGIC:='0';

if(Clk='0')then

signal m: STD_LOGIC_VECTOR(0 to 1);

if(d1'event and d1 = '0')then

signal

temp2 \le temp2 + 1;

DB,DB2,DB3,DB4,DB5,DB6,DB7,DB8,DB9:STD_LOGIC_VECTOR(

if(temp2=3)then

3 DOWNTO 0);

temp2<=3; end if; end if;

signal

else

FO,FO1,FO2,FO3,FO4,FO5,FO6,FO7,FO8:STD_LOGIC_VECTOR(3

temp2<=0; end if; end if;

DOWNTO 0);

if(temp2=2)then

signal temp1: integer range 0 to 3;

sc2<= '1';

signal temp2: integer range 0 to 5;

else

signal temp3: integer range 0 to 50;

sc2<= '0';

signal temp5: integer range 0 to 150;

end if:

signal temp4: integer range 0 to 4;

end process;

signal btemp: integer range 0 to 4000000;

signal lcdcnt: integer range 0 to 164;

----high freqn senc -----

process(nxt,Clk,d1)

signal lcdcnt1: integer range 0 to 144;

begin

begin

if(nxt='1')then

----board clock ----50M-----

if(Clk='0')then

process(bclk)

if(d1'event and d1 = '0')then

temp3 \le temp3 + 1;

begin

if(bclk'event and bclk = '0')then

if(temp3=50)then

btemp<= btemp+1;</pre>

temp3<=50; end if; end if;

if(btemp>=2000000)then

else

clk<='1';

temp3<=0; end if; end if;

else

if(temp3=48)then

clk<='0'; end if; end if;

sc3<= '1';

end process;

else

sc3<= '0';

---clock divider---

end if;

end process;

process(a)

begin

if(a'event and a = 0)then

----high high

freqn senc ----

process(nxt,Clk,d1)

temp4 \le temp4 + 1;

if(temp4>=2)then

begin

d1<='1';

if(nxt='1')then

else

if(Clk='0')then

if(d1'event and d1 = '0')then

d1<='0'; end if; end if;

temp5 \le temp5 + 1;

end process;

if(temp5=100)then

temp5<=100; end if; end if;

-----signal start-----

process(rst)

else

temp5<=0; end if; end if;

begin

if(rst='1')then

temp<='0';

if(temp5=98)then

elsif(Clk'event and Clk = '1')then

sc4<= '1':

temp<= '1';

else

end if;

sc4<= '0';

```

# International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

```

end if;

case lcdcnt is ------higher first-----then lower--

when 16 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0'

end process;

when 17 => RS<= '0'; RW<= '0'; E<= '1'; DB<= "0000";

when 18 \Rightarrow RS \le '0'; RW \le '0'; E \le '0'; DB \le ''0000'';

----lower cutoff-----

q \le sc2 \text{ nor } q1 ; q1 \le sc3 \text{ nor } q;

when 19 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0000'';

do \le not q; do1 \le not q1;

when 20 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0'

when 21 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0010'';

process(do,sc1)

when 22 => RS<= '0'; RW<= '0'; E<= '0'; DB<= "1000"

if(do='0')then

when 23 \Rightarrow RS \le '0'; RW \le '0'; E \le '1'; DB \le "1000";

when 24 \Rightarrow RS \le '0'; RW \le '0'; E \le '0'; DB \le "0010"; --funct

m0 \le 0':

elsif(sc1='1')then

when 25 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0010'';

m0 \le '1'; end if;

when 26 \Rightarrow RS \le '0'; RW \le '0'; E \le '0'; DB \le "1000";

when 27 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 1000'';

end process;

when 28 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0000''; --entry mod

----higher cutoff-----

when 29 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0000'';

q2 \le sc3 \text{ nor } q3; q3 \le sc4 \text{ nor } q2;

when 30 => RS<= '0'; RW<= '0'; E<= '0'; DB<= "0110";

do2 \le not q2; do3 \le not q3;

when 31 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0110'';

when 32 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0000''; -display on

process(do2,sc1)

when 33 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0000'';

begin

if(do2='0')then

when 34 \Rightarrow RS <= '0'; RW <= '0'; E <= '0'; DB <= "1100";

when 35 \Rightarrow RS \le '0'; RW \le '0'; E \le '1'; DB \le "1100";

m1 <= '0'

elsif(sc1='1')then

when 36 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0000'';--clear display

when 37 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0'

m1 \le '1'; end if;

when 38 \Rightarrow RS <= '0'; RW <= '0'; E <= '0'; DB <= "0001";

when 39 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0001'';

end process;

----lower cutoff -----

when 40 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0101''; -- W

process(do1,sc1)

when 41 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

when 42 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0111";

begin

if(sc2='1')then

when 43 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le ''0111''

if(do1='0')then

when 44 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0100''; -- E

m2 \le '0';

when 45 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when 46 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101";

else

m2 \le '1'; end if; end if;

when 47 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

when 48 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0100"; -- L

end process;

when 49 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when 50 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "1100";

when 51 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1100";

when 52 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1011";

process(m0,m1,m2,ls,hs,bs)

when 53 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "1011";

begin

-low output-----

when 54 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0000'';

when 55 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

if(ls='1')then

lo<= (not m0) and (not m2)and temp;

when 56 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0100"; -- C

lps<= not lo and nxt;

when 57 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le ''0100'';

end if;

when 58 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0011";

--high output--

when 59 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0011";

if(hs='1')then

when 60 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0100''; --

ho <= (not m0) and (not m2) and temp;

when 61 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le ''0100'';

hps<= ho and nxt;

end if:

when 62 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "1111";

when 63 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "1111";

-----band output-----

if(bs='1')then

when 64 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; --

m(0) \le m(1) \le m(1) \le m(1)

when 65 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

end if:

when 66 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1101";

case m is

when "01" => dof <= '1';

when 67 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1101";

when others \Rightarrow dof \Leftarrow '0';

when 68 => RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; --

end case:

bndpass <= dof and nxt;

when 69 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

when 70 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101";

end process;

when 71 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le ''0101'';

when 72 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1010"; -- Space

process(Clk)

when 73 => RS <= '1'; RW <= '0'; E <= '1'; DB <= "1010";

when 74 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0000";

begin

if(ls='0')then

when 75 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

if(hs='0')then

when 76 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101"; -- T

if(bs='0')then

when 77 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

if(Clk'event and Clk = '0')then

when 78 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0100'';

lcdcnt<= lcdcnt+1:

when 79 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

if(lcdcnt=164)then

when 80 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0100"; -- O

lcdcnt<=0;

when 81 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when 82 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1111";

end if:

when 83 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "1111";

end if:

when 84 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1010"; -- Space

```

# International Journal of Advanced Research in Computer and Communication Engineering

#### ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

```

when 85 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "1010";

when 151 => RS <= '1'; RW <= '0'; E <= '1'; DB <= "0010";

when 86 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0000";

when 152=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0010";

when 87 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

when 153=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "0001";-- display shift

when 88 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0101''; -- V

when 89 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

when 154=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "0001";

when 90 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0110";

when 155=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "1100";

when 91 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0110";

when 156=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "1100";

when 92 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; -- H

when 157=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "0001";-- display shift

when 93 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

when 94 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "1000";

when 158=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "0001";

when 159=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "1000";

when 95 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1000";

when 96 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- D

when 160=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "1000";

when 97 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 161=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "0001";-- when 162=>

when 98 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100";

RS<= '0'; RW<= '0'; E<= '1'; DB<= "0001";

when 99 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when 163=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "1000";

when 100=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- L

when 164=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "1000";

when 101=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when others =>null:

when 102=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1100";

when 103=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1100";

end case;

when 104=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "1100";-- give 2-line--

DB1<=DB; E1<=E; RS1<=RS; RW1<= RW;

e2 \le E; rs2 \le RS; rw2 \le not RW;

address

when 105=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "1100";

end if;

when 106=> RS<= '0'; RW<= '0'; E<= '0'; DB<= "0011";

end if;

when 107=> RS<= '0'; RW<= '0'; E<= '1'; DB<= "0011";

end if;

if(ls='1' or hs = '1' or bs= '1')then

when 108=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -

if(Clk'event and Clk = '0')then

- D

lcdcnt1<= lcdcnt1+1;</pre>

when 109=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

if(lcdcnt1=144)then

when 110=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100";

lcdcnt1<=0;

when 111=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 112 => RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; -

end if:

case lcdcnt1 is ------higher first-----then lower-----

when 113=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 13 => RS <= '0'; RW <= '0'; E <= '0'; DB <= "0000"; --clear display

when 114=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1001";

when 14 \Rightarrow RS \le '0'; RW \le '0'; E \le '1'; DB \le ''0000'';

when 115=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1001";

when 15 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0001'';

when 116=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -

when 16 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0001'';

when 17 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0000''; --entry mod

- G

when 18 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0000'';

when 117=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 19 \Rightarrow RS \le 0'; RW \le 0'; E \le 0'; DB \le 0110'';

when 20 \Rightarrow RS \le '0'; RW \le '0'; E \le '1'; DB \le "0110";

when 118=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0111";

when 119=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0111";

when 21 => RS<= '0'; RW<= '0'; E<= '0'; DB<= "1000"; --give 1-line--

when 120=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- when 121=>

address

RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 22 => RS<= '0'; RW<= '0'; E<= '1'; DB<= "1000";

when 122=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1001";

when 23 \Rightarrow RS <= '0'; RW <= '0'; E <= '0'; DB <= "0001";

when 123=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1001";

when 24 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0001'';

when 124=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1010"; -- Space

when 25 => RS <= '1'; RW <= '0'; E <= '0'; DB <= DB2; -- L HB

when 125=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1010";

when 26 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB2;

when 126=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0000";

when 27 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le DB3;

when 127=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0000";

when 28 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB3;

when 128=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- F

when 29 => RS<= '1'; RW<= '0'; E<= '0'; DB<= DB4; -- O I A

when 129=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 30 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= DB4;

when 31 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le DB5;

when 130=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0110";

when 131=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0110";

when 32 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB5;

when 132=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- I

when 33 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le DB6; -- W \in N

when 133=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 34 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= DB6;

when 134=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1001";

when 35 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le DB7;

when 135=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1001"

when 36 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB7;

when 136=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- L

when 37 => RS <= '1'; RW <= '0'; E <= '0'; DB <= DB8; --

when 137=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 138=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "1100";

when 139=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "1100";

when 38 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB8;

when 140=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101"; -- T

when 39 => RS <= '1'; RW <= '0'; E <= '0'; DB <= DB9;

when 141=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 40 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le DB9;

when 142=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; when 143=>

when 41 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1011"; ---

RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 42 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1011";

when 144=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- E

when 43 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0000'';

when 145=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 44 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

when 146=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101";

when 45 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101"; --

when 147=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 148=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101"; -- R

when 46 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0101";

when 149=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 150=> RS<= '1'; RW<= '0'; E<= '0'; DB<= "0010";

when 47 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0000'';

```

### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

```

when 48 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

when 49 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; -- A

when 120 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0010";

when 50 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

when 121 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- E

when 51 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0001";

when 122 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

when 52 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0001";

when 123 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101";

when 53 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101"; -- S

when 124 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101":

when 54 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 125 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1010"; -- Space

when 55 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0011";

when 126 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1010";

when 56 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0011";

when 127 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0000";

when 57 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101"; -- S when 58

when 128 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0000";

=> RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 129 => RS<= '1'; RW<= '0'; E<= '0'; DB<= FO; -- P

when 59 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0011";

when 130 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le FO;

when 60 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0011";

when 131 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le FO1;

when 61 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "1010"; -- Space

when 132 => RS<= '1'; RW<= '0'; E<= '1'; DB<= FO1;

when 62 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "1010";

when 133 => RS <= '1'; RW <= '0'; E <= '0'; DB <= FO2; -- U

when 63 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0000";

when 134 => RS<= '1'; RW<= '0'; E<= '1'; DB<= FO2;

when 64 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0000";

when 135 => RS <= '1'; RW <= '0'; E <= '0'; DB <= FO3;

when 65 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0100"; -- F

when 136 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le FO3;

when 66 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when 137 => RS<= '1'; RW<= '0'; E<= '0'; DB<= FO4; -- T

when 67 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0110";

when 138 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le FO4;

when 68 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0110";

when 139 => RS<= '1'; RW<= '0'; E<= '0'; DB<= FO5;

when 69 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- I

when 140 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le FO5;

when 70 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 141 => RS<= '1'; RW<= '0'; E<= '0'; DB<= FO6; -- T

when 142 => RS<= '1'; RW<= '0'; E<= '1'; DB<= FO6;

when 71 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1001";

when 72 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "1001";

when 143 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le FO7;

when 73 => RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; -- L

when 144 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le FO7;

when 74 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

when others =>null;

when 75 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1100";

end case;

when 76 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "1100";

when 77 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101"; -- T

DB1 \le DB ; E1 \le E ; RS1 \le RS ; RW1 \le RW ;

when 78 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

e2<=E; rs2<=RS; rw2<= not RW;

when 79 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0100'';

end if:

when 80 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

end process:

when 81 => RS<= '0'; RW<= '0'; E<= '0'; DB<= "1100"; -- give 2-line—

process(ls,hs,bs)

when 82 => RS<= '0'; RW<= '0'; E<= '1'; DB<= "1100";

when 83 => RS <= '0'; RW <= '0'; E <= '0'; DB <= "0000";

begin

when 84 \Rightarrow RS \le 0'; RW \le 0'; E \le 1'; DB \le 0000'';

if(ls='1')then

when 85 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0100"; -- C

DB2<= "0100"; DB3<= "1100"; DB4<= "0100";

when 86 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le ''0100'';

when 87 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le ''0011'';

when 88 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0011";

DB5<= "1111"; DB6<= "0101"; DB7<= "0111";

DB8<= "1010";DB9<= "0000";

when 89 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0101"; -- U

when 90 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0101";

elsif(hs='1')then

when 91 \Rightarrow RS <= '1'; RW <= '0'; E <= '0'; DB <= "0101";

DB2<= "0100"; DB3<= "1000"; DB4<= "0100";

when 92 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

DB5<= "1001"; DB6<= "0100"; DB7<= "0111";

DB8<= "0100";DB9<= "1000";

when 93 => RS <= '1'; RW <= '0'; E <= '0'; DB <= "0101"; -- T

when 94 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0101";

when 95 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0100";

when 96 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0100";

elsif(bs='1')then

when 97 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- O

DB2<= "0100"; DB3<= "0010"; DB4<= "0100";

when 98 \Rightarrow RS <= '1'; RW <= '0'; E <= '1'; DB <= "0100";

DB5<= "0001"; DB6<= "0100"; DB7<= "1110";

when 99 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "1111";

DB8<= "0100":DB9<= "0100":

when 100 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "1111";

end if;

when 101 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- F

end process;

when 102 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

end Behavioral;

when 103 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0110";

when 104 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0110";

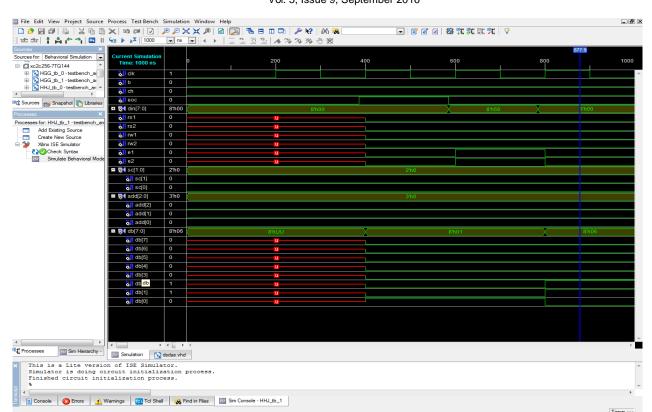

IV. SIMULATE BEHAVIORAL MODEL

when 105 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- F

when 106 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0100";

when 107 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0110":

when 108 \Rightarrow RS \le '1'; RW \le '0'; E \le '1'; DB \le "0110";

when 109 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "1010"; -- Space

when 110 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "1010";

when 111 \Rightarrow RS \le '1'; RW \le '0'; E \le '0'; DB \le "0000";

when 112 => RS<= '1'; RW<= '0'; E<= '1'; DB<= "0000";

when 113 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0100"; -- F

```

You can now run a functional simulation on the display drive module. With display\_drive.vhd highlighted in the Source window, the Process window will give all the available operations for the particular module. A VHDL file can be synthesized and then implemented through to a bit stream.

Normally, a design consists of several lower level modules wired together by a top-level file. In this instance, we are going to simulate only one lower-level module to introduce the functional simulation methodology.

when  $114 \Rightarrow RS \le '1'$ ;  $RW \le '0'$ ;  $E \le '1'$ ;  $DB \le ''0100''$ ; when 115 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0110";

when  $116 \Rightarrow RS \le '1'$ ;  $RW \le '0'$ ;  $E \le '1'$ ;  $DB \le "0110"$ ;

when  $118 \Rightarrow RS \le '1'$ :  $RW \le '0'$ :  $E \le '1'$ :  $DB \le "0101"$ :

when 119 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0010";

when 117 => RS<= '1'; RW<= '0'; E<= '0'; DB<= "0101"; -- R

# International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 5, Issue 9, September 2016

#### V. CONCLUSIONS

The proposed project-based approach encompasses whole engineering cycle, starting from specification, through modelling, simulation and verification, implementation, to performance measurement, and closing the cycle with the design improvements in order to maximize performance at minimal cost. Students have an opportunity to apply their theoretical knowledge of hardware description languages, digital design and computer architecture, and to gain real-world experience in developing IP cores. The work in small teams follows a real industry pattern, with one student designated as team leader, and instructor conducting design reviews every week. We feel that such projects are essential to educate future architects of complex systems-on-a-chip.

#### VI. REFERENCES

- Data Acquisition Linear devices Data Book National Semiconductor.

- [2] VHDL Programming by Example by Douglas L. Perry.

- [3] Circuit Design with VHDL by Volnei A. Pedroni

- [4] DIDITAL DESIGN principles & practices By John F. Wakerly

- [5] Fundamentals of Digital Logic with VHDL Design by Stephen Brownand Zvonko Vranesic

- [6] The Practical Xilinx Designer Lab Book- Prentice Hall by David Van den Bout

- [7] The Practical Xilinx Designer Lab Book- Prentice Hall by David Van den Bout

- [8] VHDL Starter's Guide.-Prentice Hall by Sudhakar Yalamanchili

- [9] Digital Designing with Programmable Logic Devices.-Prentice Hall by John W. Carter

- [10] International Journal of Advanced Research in Computer Science and Software Engineering (Volume 3, Issue 8, August 2013)

[11] Programmable Logic Design Quick Start Guide (UG500 (v1.0) May 8, 2008)

#### **BIOGRAPHIES**

**Dr. Haresh Pandya** Professor & Head, Department of Electronics, Saurashtra University, Rajkot, Gujrat, India. He obtained B.Sc, M.Sc. and Ph.D degrees from Saurashtra University-Rajkot. He specialized in the area of Electronic circuits and devices. Published large number of

technical papers in deferent international journals.

Born in December 1986, **Mr. Mahesh Rangapariya** is currently working as a Ph.D. Student & Visiting Lecturer at Department of Electronics, Saurashtra University-Rajakot. Currently pursuing Master's Degree in ELECTRONISC from Department of Electronics Saradar Patel University-

Vallabh Vidhaya Nagar. Attended Two-day "WOKRSHOPE ON EMBEDDED SYSTEMS" at Department of Electronics Saradar Patel University-Vallabh Vidhaya Nagar 2009. Attended One-day "WOKRSHOPE ON EMBEDDED SYSTEMS" at The Institution of Electronics and Telecommunication Engineers (IETE)-Rajkot 2010, he obtained B.Sc. degree in electronics from Gujarat University Ahmadabad in 2007.