# International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2016

# "Low Latency Low Complexity Compare and Decode Architecture for LTE Turbo Codes"

### Aaquib Javed<sup>1</sup>, Vijay L. Agrawal<sup>2</sup>

P.G Student, Electronics and Telecommunication Department, HVPM's College of Engineering and Technology Amravati, India<sup>1</sup>

Professor, Electronics and Telecommunication Department, HVPM's College of Engineering and Technology Amravati, India<sup>2</sup>

**Abstract:** A new architecture for matching the data protected with an error-correcting code (ECC) is presented in this brief to reduce latency and complexity. Based on the fact that the codeword of an ECC is usually represented in a systematic form consisting of the raw data and the parity information generated by encoding, the proposed architecture parallelizes the comparison of the data and that of the parity information. To further reduce the latency and complexity, in addition, a new butterfly-formed weight accumulator (BWA) is proposed for the efficient computation of the Hamming distance. Grounded on the BWA, the proposed architecture examines whether the incoming data matches the stored data if a certain number of erroneous bits are corrected. For a (40, 33) code, the proposed architecture reduces the latency and the hardware complexity by, compared with the most recent implementation. the proposed architecture reduces the latency and the hardware complexity by ~32% and 9%, respectively, compared with the most recent implementation.

**Keywords:** Reduce the latency, less complexity, High-speed access, Communication Decoding system.

#### 1. INTRODUCTION

components that are devised to increase the system performance, e.g., caches and TLBs, whose outputs determine the flow of the succeeding operations in a pipeline. The circuit, therefore, must be designed to have as low latency as possible, or the components will be deteriorated.

As recent computers employ error-correcting codes (ECCs) to protect data and improve reliability, complicated decoding procedure, which must precede the data comparison, elongates the critical path and exacerbates the complexity overhead. Despite the need for sophisticated designs as described, the works that cope with the problem are not widely known in the literature since it has been usually treated within industries for their products. Recently, however, trigered the attraction of more and more attentions from the academic field. The most recent solution for the matching problem is the direct compare method, which encodes the incoming data and then compares it with the retrieved data that has been encoded as well. Therefore, the method eliminates the complex decoding from the critical path. In performing the comparison, the method does not examine whether the retrieved data is exactly the same as the incoming data.

Data comparison is widely used in computing systems to Instead, it checks if the retrieved data resides in the error perform many operations such as the tag matching in a correctable range of the codeword corresponding to the cache memory and the virtual-to-physical address incoming data. As the checking necessitates an additional translation in a translation look a side buffer (TLB). The circuit to compute the Hamming distance i.e. the numbers data comparison usually resides in the critical path of the of different bits between the two code words, the saturate adder (SA) as a basic building block for calculating the Hamming distance. However, a practical ECC codeword is usually represented in a systematic form in which the data and parity parts are completely separated from each other. In addition, as the SA always forces its output not to be disqualified from serving as accelerators and the overall greater than the number of detectable errors by more than performance of the whole system would be severely one, it contributes to the increase of the entire circuit complexity.

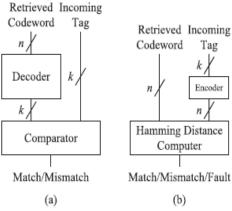

Fig. 1(a) Decode-and-compare architecture and (b) encode-and-compare architecture

#### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2016

#### 2. LITERATURE REVIEW

The decode-and-compare architecture, the n-bit retrieved August 24, 2006; revised December 20, 2006. codeword should first be decoded to extract the original kbit tag. The extracted k-bit tag is then compared with the project's work and research till date:

# decision viterbi algorithm in vhdl

Susrutha Babu Sukhavasi, Suparshya Babu Sukhavasi, G. Fettweis and H. Meyr, "Cascaded feedforward Dr. Habibulla Khan, IEEE Chiranjeevi Pilla/ International architectures for parallel Viterbi decoding," in Proc. IEEE Journal of Engineering Research and Applications Int. Sym. Circuits Syst., May 1990, pp. 978–981. (IJERA) ISSN: 2248-9622 Vol. 2, Issue 3, May-Jun 2012 We first briefly describe the algorithms of convolution The Viterbi-Algorithm (VA) is a common application of encoder and hard decision Viterbi decoder. The focus of this work is towards developing an application specific design methodology for low power solutions. The methodology starts from high level models which can be used for hardware solution and proceeds towards high performance hardware solutions. The methodology starts from algorithmic level, concentrating on the functional correctness rather than on implementation architecture. The effect on performance due to variation in parameters especially in wireless systems.

#### II Reed-Solomon Turbo Product Codes for Optical met by very different architectures. Communications: From Code Optimization to **Decoder Design**

Institut TELECOM, TELECOM Bretagne, CNRS Lab-STICC, Technopoole Brest-Iroise, CS 83818, 29238 Brest In the decode-and-compare architecture, the n-bit retrieved 22 April 2008

practical interest. Although this has been a major step complexity overhead is not negligible. forward, there is still a need for improvement in forward- Note that decoding is usually more complex and takes flexibility, throughput, and cost.

# III Turbo and Turbo-Like Codes: Principles and **Applications in Telecommunication**

K. Gracie is with the Communications Research Centre • Most complicated processing elements (CRC) Ottawa, ON K2H 8S2, Canada. M.-H. Hamon is • More complexity

with France Telecom Research and Development, 35512 Cesson- Se'vigne' Cedex, France Manuscript received

For decades, the de facto standard for forward error correction was a convolution code decoded with the k-bit tag field of an incoming address to determine Viterbi algorithm, often concatenated with another code whether the tags are matched or not. As the retrieved (e.g., a Reed-Solomon code). But since the introduction of codeword should go through the decoder before being turbo codes in 1993, much more powerful codes referred compared with the incoming tag, the critical path is too to collectively as turbo and turbo-like codes have eclipsed long to be employed in a practical cache system designed classical methods. These powerful error-correcting for high-speed access. Since the decoder is one of the most techniques achieve excellent error-rate performance that complicated processing elements, in addition, the can closely approach Shannon's channel capacity limit. complexity overhead is not negligible. The following The lure of these large coding gains has resulted in their section will point out the evolution of the proposed incorporation into a widening array of telecommunications standards and systems.

#### I Performance evaluation of turbo codes using hard IV Cascaded feed forward architectures for parallel viterbi decoding

dynamic programming. Since it contains a nonlinear feedback loop (ACS-feedback, ACS: add-compare-select), this loop is the bottleneck in high data implementations. In this paper we show asymptotically the ACS-feedback no longer has to be processed recursively, i.e. there is no feedback, resulting in negligible performance loss. This can be exploited to derive purely feed forward architectures for Viterbi decoding, such that a modular cascadable implementation like frame length, number of iterations, type of encoding results. By designing one cascadable module, any speedup scheme. Turbo codes are used for error protection, can be achieved simply by adding modules to the implementation. It is shown that optimization criteria, e.g. minimum latency or maximum hardware efficiency, are

#### 3. PROBLEM DEFINITION

Cedex 3, France Correspondence should be addressed to codeword should first be decoded to extract the original k-Rapha el Le Bidan Received 31 October 2007; Accepted bit tag. The extracted k-bit tag is then compared with the k-bit tag field of an incoming address to determine The field of channel coding has undergone major whether the tags are matched or not. As the retrieved advances for the last twenty years. With the invention of codeword should go through the decoder before being turbo codes followed by the rediscovery of low-density compared with the incoming tag, the critical path is too parity check (LDPC) codes, it is now possible to approach long to be employed in a practical cache system designed the fundamental limit of channel capacity within a few for high-speed access. Since the decoder is one of the most tenths of a decibel over several channel models of complicated processing elements, in addition, the

error correction (FEC), notably in terms of code more time than encoding as it encompasses a series of error detection or syndrome calculation, and error correction.

- The critical path is too long

#### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2016

#### 4. RESEARCH METHODOLOGY

practice, the ECC codeword is of a systematic form in which the data and parity parts are completely separated. As the data part of a systematic codeword is exactly the The realization of this project will solve most of the same as the incoming tag field, it is immediately available difficulties discussed above and in the problem definition for comparison while the parity part becomes available only after the encoding is completed.

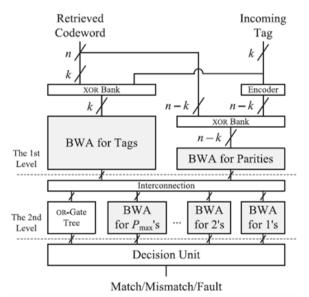

The proposed architecture grounded on the data path o High-speed access design is shown in Fig. 1. It contains multiple butterflyformed weight accumulators (BWAs) proposed to improve Ocommunication Decoding systems the latency and complexity of the Hamming distance computation. The basic function of the BWA is to count the number of 1's among its input bits.

#### • SYSTEM BLOCK DIAGRAM:

Fig. 1 Proposed architecture optimized for systematic code words

### 5. IMPLICATION

For a set of four codes including the (31, 25) code quoted, We measured the metrics at the gate-level first and then implemented the circuits in a 0.13-µm CMOS technology to provide more realistic results by deliberating some practical factors, e.g., gate sizing and wiring delays. The latency is measured from the time when the incoming address is completely encoded. As the critical path starts from the arrival of the incoming address to a cache memory, the encoding delay must be, however, included in the latency computation. Performing post layout simulations and equivalent gate counts are measured by counting a two-input NAND as one.

The latencies of the SA-based architecture and the proposed one are dominated by SAs and HAs, In the SA (saturate adder)-based architecture, the respectively. As the bit-width doubles, at least one more comparison of two code words is invoked after the stage of SAs or HAs needs to be added. Since the critical incoming tag is encoded. Therefore, the critical path path of a HA consists of only one gate while that of a SA consists of a series of the encoding and the n-bit has several gates, the proposed architecture achieves lower comparison. However, it did not consider the fact that, in latency than its SA-based counterpart, especially for long codewords.

section. This project will have following results:

- o Reduce the latency

- Less complexity

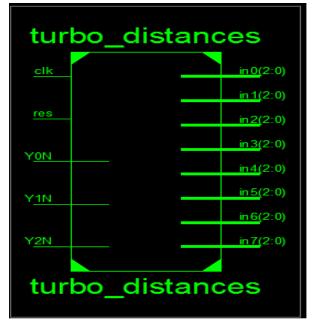

Fig. 2 turbo distances

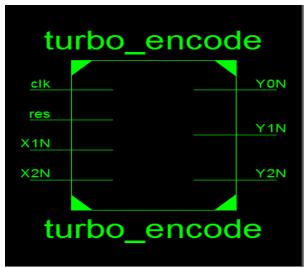

Fig. 3 turbo encoder

#### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2016

#### REFERENCES

- [1] Susrutha Babu Sukhavasi, Suparshya Babu Sukhavasi, Dr. Habibulla Khan," Performance evaluation of turbo codes using hard decision viterbi algorithm in vhdl ,"IEEE Chiranjeevi Pilla/ International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 Vol. 2, Issue 3, May-Jun 2012

- [2] Raphael Le Bidan, Camille Leroux, Christophe Jego, Patrick Adde, and Ramesh Pyndiah, "Reed-Solomon Turbo Product Codes for Optical Communications: From Code Optimization to Decoder Design," Institute TELECOM, TELECOM Bretagne, CNRS Lab-STICC, Technop'ole Brest-Iroise, CS 83818, 29238 Brest Cedex 3, France Correspondence should be addressed to Rapha el Le Bidan Received 31 October 2007; Accepted 22 April 2008

- [3] K. Gracie is with the Communications Research Centre (CRC) Ottawa," Turbo and Turbo-Like Codes: Principles and Applications in Telecommunication," ON K2H 8S2, Canada. M.-H. Hamon is with France Telecom Research and Development, 35512 Cesson-Se'vigne' Cedex, France Manuscript received August 24, 2006; revised December 20, 2006.

- [4] Byeong Yong Kong, Jihyuck Jo, Hyewon Jeong, Mina Hwang, "Low-Complexity Low-Latency Architecture for Matching of Data Encoded With Hard Systematic Error-Correcting Codes," Manuscript received January 14, 2013; revised May 22, 2013; accepted July 25, 2013. Date of publication August 21, 2013; date of current version June 23, 2014.IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 22, NO. 7, JULY 2014

- [5] G. Fettweis and H. Meyr, "Cascaded feedforward architectures for parallel Viterbi decoding," in Proc. IEEE Int. Sym. Circuits Syst., May 1990, pp. 978–981.