International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 5, Issue 10, October 2016

# Design, Analysis & Simulation of 30 nm Cylindrical Gate all around MOSFET

Tarun Kumar Sachdeva<sup>1</sup>, Dr. S.K. Aggarwal<sup>2</sup>, Dr. Alok K Kushwaha<sup>3</sup>

Research Scholar, EEE Department, YMCAUST, Faridabad<sup>1</sup>

Professor, EEE Department, YMCAUST, Faridabad<sup>2</sup>

Professor& Asst. Dean Academic, Waljat College of Applied Science, Muscat, Oman<sup>3</sup>

Abstract: Cylindrical gate all around (GAA) MOSFET is a drastic invention and a potential candidate to replace conventional MOSFET, as it introduces new direction for transistor scaling without hindering the device performance. In this work, electrical characteristics of cylindrical GAA (CGAA) MOSFET at 50nm channel length (Lg), 10nm channel thickness (tsi) are systematically analysed. Various electrical characteristics such as On current  $(I_{ON})$ , subthreshold leakage current  $(I_{OFF})$ , the threshold voltage  $(V_{th})$ , DIBL are calculated and analysed at various device design parameters. All the device performances of Cylindrical GAA MOSFETs are investigated through Atlas device simulator from Silva co.

Keywords: Cylindrical gate all around (GAA) MOSFET, subthreshold leakage current (I<sub>OFF</sub>),

#### **1. INTRODUCTION**

The aggressivescaling of CMOS technology has been the Also various important device parameters like threshold attention of electronic industry in the last few decades. voltage ( $V_{th}$ ), and on-off ratio ( $I_{ON}/I_{OFF}$ ), are very much The main propel for scaling is the necessity of achieving sensitive to the device geometry such as channel length higher packing density, intensifying the performance of (Lg), channel thickness (tsi). In this paper, various electrical SOI chips, and cost effective electronic devices. However, parameters, like threshold voltage  $(V_{th})$ , drain current  $(I_D)$ the scaling of the CMOS transistor comes on the cost of are analytically presented. raising several flawed such as drain-induced barrier lowering, hot carrier effects etc.

These flaws lso known as short channel effects, have a The schematic diagram of the Cylindrical GAA (CGAA) large impact on the performance on the circuits, and performance therefore thev limit the expected enhancement [1]-[2].To overcome these flaws, new circuits and design techniques are mandatory to utilize the edge of the newer technologies.

Some multi-gate silicon on insulator (SOI) technology has also been proposed for promising solution to replace the conventional MOSFET [3]. However, the cylindrical gate all around (CGAA) MOSFET is one of the new technologieswhich further enables the scaling without hampering the device performance [4][5].Since due to higher drive current and shorter length, Cylindrical GAA MOSFETs can achieve higher packing density as compared to the other multiple-gate MOSFETs.

Also, cylindrical gate-all-around (CGAA) MOSFETs in which the gate oxide and the gate electrodes wrap around the channel region exhibit excellent electrostatic control of the channel, no floating body effect, stoutness against SCEs, better scaling options, ideal sub threshold swing as compared to other multi-gate MOSFETs [6]. Hence, the CGAA MOSFETs are a brilliant solution for nanoscale technology CMOS devices [7].

#### 2. DEVICE STRUCTURE AND SPECIFICATION

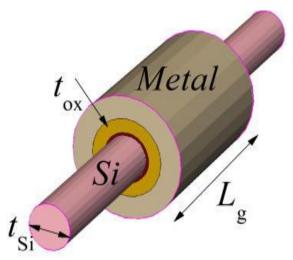

MOSFET structures used for simulation is shown in Fig. 1. This structure is implemented using Atlas Silvaco tool. The radial directions are assumed to be along radius and lateral direction along z-axis of the cylinder as shown in Fig. 1.

Fig 1: Schematic Structure of Cylindrical Gate All Around (GAA) MOSFET

### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified Vol. 5, Issue 10, October 2016

MOSFETs having n-type channels. The Length of the gate used in the simulation to avoid abrupt junction. The metal (Lg) is 30nm with work function 4.4 eV. We have taken gate work function  $\phi_{M=}$  4.4 eV has been considered. diameter  $(t_{si})$  of 10nm. We use SiO<sub>2</sub> in gate oxide with thickness (tox) 1 nm.

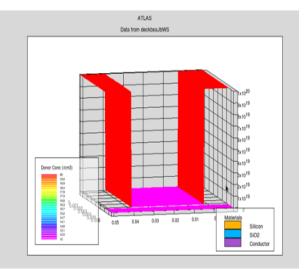

The details of device physical parameters used in the Fig 4 shows the Uniform donor(N<sub>D</sub>)doping profileplot structure are shown in Table 1.SOI substrate in GAA between source and drain of fixed charges  $1 \times 10^{20}$  cm-3 is

Table 1: Device Dimensions & Dopings

| Parameter                         | Value                                     |

|-----------------------------------|-------------------------------------------|

| Gate Length (Lg)                  | 30nm                                      |

| Radius (t <sub>si</sub> /2)       | 5nm                                       |

| OxideThickness (t <sub>ox</sub> ) | 1nm                                       |

| Channel Doping                    | $1.0 \mathrm{x} 10^{18} \mathrm{cm}^{-3}$ |

| Source Doping (N <sub>D</sub> )   | $1.0 \mathrm{x} 10^{20} \mathrm{cm}^{-3}$ |

| Drain Doping (N <sub>D</sub> )    | $1.0 \mathrm{x} 10^{20} \mathrm{cm}^{-3}$ |

The source/drain extension doping profile was set as Gaussian with the peak concentration of  $1.0 \times 10^{20}$  cm<sup>-3</sup>.

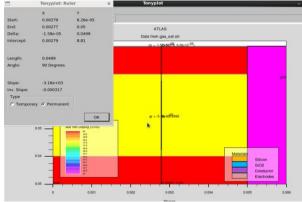

Fig 2 shows the cross sectional view of cylindricalGAA MOSFET of channel length 30 nm has been used in simulation.

Fig 2: Cross sectional view of GAA structure for channel length (Lg)

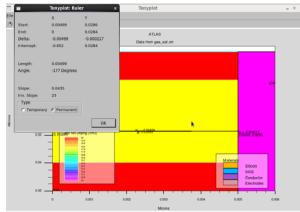

Fig 3 shows the cross sectional view of GAA structure for silicon thickness of radius( $t_{si}/2$ ) 5nm and oxide thickness of 1nm has been used in simulation.

Fig 3: Cross sectional view of GAA structure for Oxide thickness  $(t_{ox})$  Silicon thickness  $(t_{si})$

Fig 4: Donor Concentration Graph

#### 3. RESULTS AND DISCUSSION

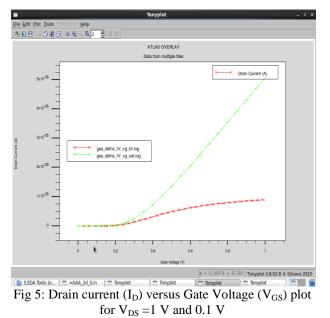

Fig 5 demonstrates the transfer characteristics of GAA MOSFETs. Simulation was done with various drain voltages.

GAA MOSFET threshold voltage (Vth) extraction was performed based on a constant current definition which is universally adapted to measure. During simulation we consider a constant current level of 1x10<sup>-7</sup> A/ m.Fig 6 shows the transfer characteristics of GAA MOSFET for various Gate voltages. DIBL was defined as the difference in threshold voltage when the drain voltage was increased from 0.1 to 1 V.

## International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2016

Fig 6: Drain Current ( $I_D$ ) in log scale as a function of Gate Voltage ( $V_{GS}$ ) for  $V_{DS}$  =1 V and 0.1 V

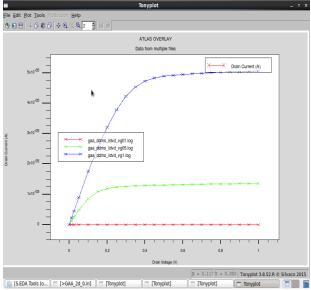

Driving current  $I_{ON}$  and  $I_{OFF}$  were analysed for various Gate Voltage (V<sub>GS</sub>). Fig 7 shows the driving current  $I_{ON}$  was obtained at V<sub>G</sub>=1.0 V and  $I_{OFF}$  was obtained at V<sub>G</sub>=0.1 V.

The Result of Simulation were summarised in Table II.

| Table II: Simulated value of Electrical Characteristics of |  |

|------------------------------------------------------------|--|

| the structure                                              |  |

| Parameter        | Value           |

|------------------|-----------------|

| V <sub>TH</sub>  | 0.17 V          |

| SS               | 0.06159 mV/dec  |

| DIBL             | 0. 0182544 mV/V |

| I <sub>ON</sub>  | 7.74e-5 A       |

| I <sub>OFF</sub> | 1.74e-10 A      |

#### **4. CONCLUSION**

To reduce the short channel effects (SCEs) and improving the device reliability, GAA MOSFET is proposed. GAA MOSFETs showsrefinement in almost every aspect such as subthreshold swing (SS), OFF state current (IOFF) and DIBL. Better suppression of SCEs and an improvement in the device reliability has been observed through the simulation results.

#### REFERENCES

- K. K. Young, "Short-channel effect in fully depleted SOI MOSFETs", IEEE Trans. Electron Devices, vol. 36, no. 2, pp. 399– 402, 1989.

- [2] S. Bangsaruntip, G. M. Cohen, A. Majumdar, and J. W. Sleight, "Universality of short-channel effects in undoped-body silicon nanowire MOSFETs", IEEE Electron Device Lett., vol. 31, no. 9, pp. 903–905, 2010

- [3] V. M. Srivastava, K. S. Yadav, and G. Singh, "Design and performance analysis of double-gate MOSFET over single-gate MOSFET for RF switch", Microelectronics J., vol. 42, no. 3, pp. 527–534, 2011.

- [4] M. R. Kumar, S. K. Mohapatra, K. P. Pradhan, and P. K. Sahu, "A simple analytical center potential model for cylindrical gate all around (CGAA) MOSFET", J. Electron Devices, vol. 19, pp. 1648– 1653, 2014.

- [5] H. Abd-Elhamid, B. Iñiguez, D. Jiménez, J. Roig, J. Pallarès, and L. F. Marsal, "Two-dimensional analytical threshold voltage roll-off and subthreshold swing models for undoped cylindrical gate all around MOSFET", Solid. State. Electron., vol. 50, no. 5, pp. 805–812, 2006.

- [6] Y. Pratap, P. Ghosh, S. Haldar, R. S. Gupta, and M. Gupta, "An analytical subthreshold current modeling of cylindrical gate all around (CGAA) MOSFET incorporating the influence of device design engineering", Microelectronics J., vol. 45, no. 4, pp. 408– 415, 2014.

- [7] L. Zhang, C. Ma, J. He, X. Lin, and M. Chan, "Analytical solution of subthreshold channel potential of gate underlap cylindrical gateall-around MOSFET", Solid. State. Electron., vol. 54, no. 8, pp. 806–808, 2010.