International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified Vol. 7, Issue 7, July 2018

# Analysis of Low Power and High Speed Double Tail Comparator using FinFET Technology

Shwet Kumar<sup>1</sup>, Sanjeev Srivastav<sup>2</sup>, Satyarth Tiwari<sup>3</sup>

M. Tech Scholar, ECE Department, RKDF College of Engineering, Bhopal, M.P., India<sup>1</sup>

Professor, ECE Department, RKDF College of Engineering, Bhopal, M.P., India<sup>2</sup>

Assistant Professor, ECE Department, RKDF College of Engineering, Bhopal, M.P., India<sup>3</sup>

**Abstract:** In conventional double tail comparators, Kick-back noise is produced and the circuit requires high input impedance. Due to aggressive scaling of MOS, short channel effects occur and there is a need of substitutes like FinFETS. In this paper, we have designed double tail comparator by using FinFET technology in shorted gate mode. It is seen from results that the power and delay are reduced in a large quantity maintaining the output waveforms to the previous one. This improves efficiency of the system and noise tolerance and leakage current are also reduced. This can be beneficial for the Analog to Digital Converters, reference voltage comparison.

Keywords: FinFET, Double tail Comparator, 32nm, MOSFET

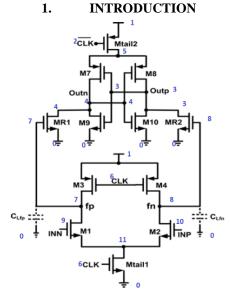

Figure 1: Conventional double tail comparator

In figure 1 conventional double tail comparator is shown. This is also implemented using FinFET Technology to check feasibility of the circuit. The working of the double tail comparator is explained below.

**1.1 Operation of Double Tail Comparator:** The schematic diagram of the conventional dynamic comparator widely used in A/D converters, with high input impedance, rail-to-rail output swing, and no static power consumption [1],[5] is shown in Fig. 1. The operation of the comparator is as follows. During the reset phase when CLK = 0 and Mtail is off, reset transistors (M7–M8) pull both output nodes Outn and Outp to VDD to define a start condition and to have a valid logical level during reset. In the comparison phase, when CLK = VDD, transistors M7 and M8 are off, and Mtail is on. Output voltages (Outp, Outn), which had been pre-charged to VDD, start to discharge with different discharging rates depending on the corresponding input voltage (INN/INP). Assuming the case where VINP > VINN, Outp discharges faster than Outn, hence when Outp (discharged by transistor M2 drain current), falls down to VDD–|Vthp| before Outn (discharged by transistor M1 drain current), the corresponding pMOS transistor (M5) will turn on initiating the latch regeneration caused by back-to-back inverters (M3, M5 and M4, M6). Thus, Outn pulls to VDD and Outp discharges to ground. If VINP < VINN, the circuits works vice versa. Figure 2 shows proposed circuit of FinFET technology double tail comparator. In this 4 transistors are added and two signals fn and fb for stacking which reduces power consumption. But in 32nm, short channel effects prevent further improvement; this motivates to change the transistor technology.

# International Journal of Advanced Research in Computer and Communication Engineering

Vol. 7, Issue 7, July 2018

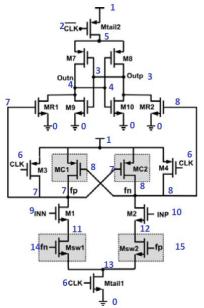

Figure 2: Proposed circuit using FinFET

Due to the better performance of double-tail architecture in low-voltage applications [2], the proposed comparator is designed based on the double-tail structure. The main idea of the proposed comparator is to increase Vfn/fp in order to increase the latch regeneration speed [4]. For this purpose, two control transistors (Mc1 and Mc2) have been added to the first stage in parallel to M3/M4 transistors but in a cross-coupled manner.

The operation of the proposed comparator is as follows:

During reset phase (CLK = 0, Mtail1 and Mtail2 are off, avoiding static power), M3 and M4 pulls both fn and fp nodes to VDD, hence transistor Mc1 and Mc2 are cut off. Intermediate stage transistors, MR1 and MR2, reset both latch outputs to ground. During decision-making phase (CLK = VDD, Mtail1, and Mtail2 are on), transistors M3 and M4 turn off. Furthermore, at the beginning of this phase, the control transistors are still off (since fn and fp are about VDD). Thus, fn and fp start to drop with different rates according to the input voltages. Suppose VINP > VINN, thus fn drops faster than fp, (since M2 provides more current than M1). As long as fn continues falling, the corresponding pMOS control transistor (Mc1 in this case) starts to turn on, pulling fp node back to the VDD; so another control transistor (Mc2) remains off, allowing fn to be discharged completely. In other words, unlike conventional double-tail dynamic comparator, in which Vfn/fp is just a function of input transistor trans-conductance and input voltage difference in the proposed structure as soon as the comparator detects that for instance node fn discharges faster, a pMOS transistor (Mc1) turns on, pulling the other node fp back to the VDD. Therefore by the time passing, the difference between fn and fp (Vfn/fp) increases in an exponential manner, leading to the reduction of latch regeneration time . Despite the effectiveness of the proposed idea, one of the points which should be considered is that in this circuit, when one of the control transistors (e.g., Mc1) turns on, a current from VDD is drawn to the ground via input and tail transistor (e.g., Mc1, M1, and Mtail1), resulting in static power consumption. To overcome this issue, two nMOS switches are used below the input transistors [Msw1 and Msw2]. At the beginning of the decision making phase, due to the fact that both fn and fp nodes have been pre-charged to VDD (during the reset phase), both switches are closed and fn and fp start to drop with different discharging rates. As soon as the comparator detects that one of the fn/fp nodes is discharging faster, control transistors will act in a way to increase their voltage difference. Suppose that fp is pulling up to the VDD and fn should be discharged completely, hence the switch in the charging path of fp will be opened (in order to prevent any current drawn from VDD) but the other switch connected to fn will be closed to allow the complete discharge of fn node. In other words, the operation of the control transistors with the switches emulates the operation of the latch.

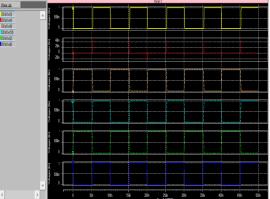

## 2. SIMULATION RESULTS

The simulations are performed on HSPICE Software, BSIM CMG FinFET Model is used and PTM BSIM MOSFET in 32nm technology. The output waveform of double tail comparator is shown in Figure 3 below. The signal 2 and 6 are clock bar and clock, 9 and 10 are inputs, and 3 and 4 are outputs of the comparator. It is seen that by using FInFET technology same output can be achieved with lower consumption and propagation delay.

## IJARCCE

### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 7, Issue 7, July 2018

Figure 3: Output Waveform of Comparator

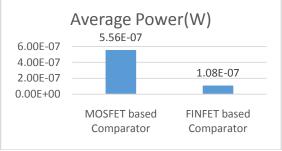

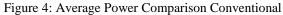

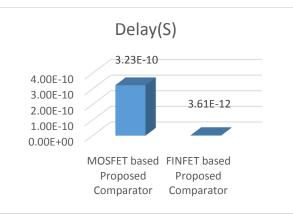

**2.1** Average Power & Delay Calculations: Figure 4 and Figure 5 shows average power results of MOSFET and FinFET based double tail comparator in conventional and proposed devices for double tail comparator.

Figure 5: Average Power Comparison Proposed

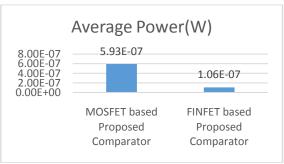

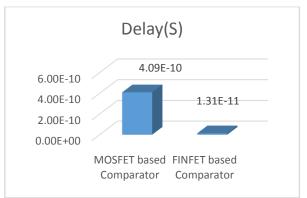

Figure 6 and Figure 7 shows delay results of MOSFET and FinFET based double tail comparator in conventional and proposed devices for double tail comparator.

Figure 6: Delay Comparison Conventional

#### ISSN (Online) 2278-1021 ISSN (Print) 2319-5940

### International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 7, Issue 7, July 2018

IJARCCE

Figure 7: Delay Comparison Conventional Proposed

Table 1 and Table 2 shows average power and delay results of MOSFET and FinFET based double tail comparator in conventional and proposed devices for double tail comparator.

Table 1. Results of Conventional Comparator

| Table 1. Results of Conventional Comparator |            |       |            |       |  |

|---------------------------------------------|------------|-------|------------|-------|--|

|                                             | MOSFET     | based | FINFET     | based |  |

| circuit1                                    | Comparator |       | Comparator |       |  |

| Average                                     |            |       |            |       |  |

| Power(W)                                    | 5.56E-07   |       | 1.08E-07   |       |  |

| Delay(S)                                    | 4.09E-10   |       | 1.31E-11   |       |  |

| Demy(D)                                     | T.07L-10   |       | 1.51L-11   |       |  |

| Table 2. Results of Hoposed Comparator |                     |                     |  |  |  |

|----------------------------------------|---------------------|---------------------|--|--|--|

|                                        | MOSFET based        | FINFET based        |  |  |  |

| circuit2                               | Proposed Comparator | Proposed Comparator |  |  |  |

| Average                                |                     |                     |  |  |  |

| Power(W)                               | 5.93E-07            | 1.06E-07            |  |  |  |

| Delay(S)                               | 3.23E-10            | 3.61E-12            |  |  |  |

| Table 2: Results | of Proposed | Comparator |

|------------------|-------------|------------|

|------------------|-------------|------------|

## CONCLUSION

Simulation results show that DOUBLE TAIL COMPARATOR conventional and proposed have improved speed and a lower consumption of average power. The average power and delay is improved by 80.5 % and 96.7% respectively for conventional DOUBLE TAIL COMPARATOR MOSFET and FinFET. For proposed DOUBLE TAIL COMPARATOR, the FinFET DOUBLE TAIL COMPARATOR is improved by 82.12% in Average Power and in Delay it is improved by 98.8%.

## REFERENCES

- [1] Samaneh Babayan-Mashhadi, Student Member, IEEE, and Reza Lotfi, Member, IEEE, "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator", IEEE transactions on Very Large Scale Integration (VLSI) Systems, VOL. 22, NO. 2, FEBRUARY 2014

- [2] P. Rajesh, M. Priyanka, Nalini, M. Chandra Mouli, "AN OPTIMIZED LOW-VOLTAGE LOW-POWER DOUBLE TAIL COMPARATOR FOR HIGH-SPEED ADCS", International Journal of Advances in Engineering & Technology, June, 2016.

- [3] Dinabandhu nath Mandall., Niladri Prasad Mohapatra1, Rajendra Prasad3 , Ambika Singh1, "Analysis and Design of Low Voltage Low Power Dynamic Comparator with Reduced Delay and Power", International Journal of Engineering Research and General Science Volume 2, Issue 3, April-May 2014

- [4] Madhumathi, Ramesh Kumar, "Design And Analysis Of Low Power And High Speed Double Tail Comparator", INTERNATIONAL JOURNAL OF TECHNOLOGY ENHANCEMENTS AND EMERGING ENGINEERING RESEARCH, VOL 2, ISSUE 5, 2014

- [5] Anu, RM Singh, "Design and Analysis of a Low-Voltage Double-Tail Comparator for Flash ADC at 180nm and 90nm CMOS Technology", International Journal of Scientific & Engineering Research, Volume 6, Issue 10, October-2015

- [6] C Manoj Kumar, S Bharath, K Anusha and C Ajay Kumar, "Design of a Double Tail Dynamic Comparator for Low Power and High Speed applications", International Journal of Scientific & Engineering Research, Volume 7, Issue 3, March-2016

- [7] Chandrahash Pate, Dr. Veena C.S., Prof. Shivendra Singh, "Design of Low-Power Double Tail Dynamic Comparator", INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 2, Issue 8, August 2014

- [8] POOJA JOSHII, APARNA KARWAL2," Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator", IJVDCS, ISSN 2322-0929 Vol.04, Issue.03, March-2016

- [9] P. Raja Sekara Pandian1, Mr. M. Krishnamurthy2, "Performance Analysis of Dual Tail Comparator for Low Power Applications", IJCSMC, Vol. 3, Issue. 4, April 2014

## IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 7, Issue 7, July 2018

- [10] Vaishnavi Jumade1, Prof. Amol Boke2, "Designing of Double Tail Comparator for High Speed Application: A Review", International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395 -0056 Volume: 03 Issue: 04 | Apr-2016

- [11]Ajay N. Bhoj, and Niraj K. Jha, "Design of Logic Gates and Flip-Flops in High-performance FinFET Technology" IEEE Transactions on very large scale Integration (VLSI) systems, pp. 1-14, 2013.

- [12]R.Rajprabu, V. Arun Raj, R. Rajnarayanan, S. Sadaiyandi, V. Sivakumar, "Performance Analysis of CMOS and FinFET Logic" IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) vol. 2, no. 1), pp. 01-06, 2013

- [13] Angada B. Sachid, Chenming Hu, "A Little Known Benefit of FinFET over Planar MOSFET in High-Performance Circuits at Advanced Technology Nodes", 978-1-4673-2691-9/12 2012 IEEE

- [14] B. Doris, K. Cheng and A. Khakifirooz, Q. Liu, and M. Vinet "Device Design Considerations for Next Generation CMOS Technology: Planar FDSOI and FinFET", 978-1-4673-3082-4/13 ©2013 IEEE

- [15] Ramachandran Muralidhar, Jin Cai, Isaac Lauer, Kevin Chan, Pranita Kulkarni, Young-Hee Kim "A Comparison of Short-Channel Control in Planar Bulk and Fully Depleted Devices", IEEE ELECTRON DEVICE LETTERS, VOL. 33, NO. 6, JUNE 2012

- [16] Zhichao Lu and Jerry G. Fossum, Fellow, IEEE "Short-Channel Effects in Independent-Gate FinFETs", IEEE ELECTRON DEVICE LETTERS, VOL. 28, NO. 2, FEBRUARY 2007

- [17] A.Amara, "Planar Double gate Transistor", Springer, 2009

- [18] Jean-Pierre Colinge, "FinFETs and Other Multi-Gate Transistors", Springer, 2008