International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

# Accelerators for Gate Clock Loop Pipelining of Binary Instruction Traces

# Nandkishor Lodhi<sup>1</sup>, Anoop Kumar khambra<sup>2</sup>, Jitendra Mishra<sup>3</sup>

PG Student [Digital Communication], Department of ECE, Bhopal, India<sup>1</sup> Associate Professor, Department of ECE, Bhopal, India<sup>2</sup> Associate Professor, HOD of ECE, Bhopal, India<sup>3</sup>

**Abstract:** Data driven gating is causing area and power overheads that must be considered. To reduce the overhead, it is proposed to group several FFs to be driven by the same clock signal, generated by bring the enabling signals of the individual FFs. This may however, lower the disabling effectiveness. In a recent paper, a model for data-driven gating is developed based on the toggling activity of the constituent FFs. The optimal fan-out of a clock gate yielding maximal power savings is derived based on the average toggling statistics of the individual FFs, process technology, and cell library in use. Data driven clock gating is a popular technique used in many synchronous circuits for reducing dynamic power dissipation. When a logic unit is clock, its underlying sequential elements receive the clock signal regardless of whether they will toggle in the next cycle. In this flip-flops are grouped so that they share a common clock enabling signal to reduce the hardware overhead and power consumption.

**Keywords:** Data Driven, Logic Gates, Flip-Flops, Clock Gating, AND Clock Gating, NOR Clock Gating, Latch based Clock Gating, Clock Networks, Register, Pulse, Power Estimator, DFD and RDFD

# I. INTRODUCTION

Clock engaging signs are amazingly without a doubt knew at the structure level and along these lines can sufficiently be described and get the periods where valuable squares and modules don't ought to be planned. Those are later being normally coordinated into time enabling signs at the gateway level. Generally speaking, clock engaging signs are physically included for each FF as a part of a framework rationality. Still, when modules at a high and portal level are planned, the state moves of their concealed FFs depend on upon the data being taken care of. Take note of that the entire component control ate up by a system originates from the periods where modules' clock signs are engaged. Thusly, paying little regard to how by and large little this period is, assessing the sufficiency of clock gating requires wide reenactments and real examination of FFs flipping development.

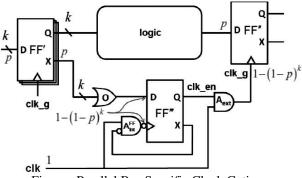

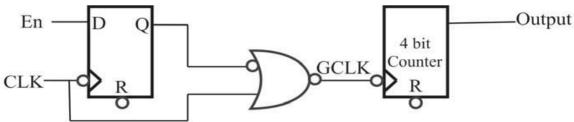

Figure : Parallel Bus Specific Clock Gating.

The auto gated flip disappointments could be executed as a utilization of Parallel Bus Specific Clock Gating (PBSC). This could be capable of drive saving from the circuits used as a part of the flip-flops for measuring the yields. An activity driven parallel transport specific CG is used to help dynamic power diminishment at RT level before combination. It picks solely a game plan of Flip-Flop (FF) to be gated by assurance, and thusly the downside of gated FF choice is diminished

International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

from exponential quality into direct. Exactly when the OBSC is associated with the look, the parts activity overabundance operations all through the clock gated entirety square measure controlled by forward exploring the circuit from the gated FF yields. These parts will be power gated manhandle the clock change hail made by OBSC the length of the utilization of RTPG will diminish dynamic discharge control. The practicable-ness examination of RTPG is predicated on our organized minimum ordinary sit out of apparatus time create.

#### DATA DRIVING CLOCK GATING

A technique called Data-driven clock gating was discussed for flip-flops (FFs). There, the clock flag driving a Flipflop, is gated when the FF's state is not subject to change in the going with clock cycle. While endeavoring to lessen the overhead of the gating technique for thinking, a couple flipflops are driven by a practically identical clock hail, made by ORing the connecting with signs of the individual flipflops. Information driven gating impacted from a brief traverse window. The aggregate deferment of the XOR, OR, bolt and the AND entryway must not assemble the setup time of the Flipflop.

Figure : Parallel Bus Specific Clock Gating.

## II. PROPOSED ALGORTHM

The use of force is significant issue in outline of computerized circuit for complex equipment with the end goal of portable correspondence and another imparting gadget. For the decrease of force utilization utilized clock gating framework. The clock gating framework lessens the utilization of force approx. (10-19%). Presently a day utilized different clock gating framework, for example, AND, NOR and hook based clock gating framework. A few procedures to lessen the dynamic power are created, of which clock gating is dominating.

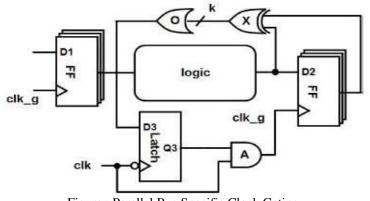

## LATCH BASED CLOCK GATING

Snare neither based mostly NOR Gated Clock arrange is showed up in Figure 3.3.3(A). Here engages banner is associated through attach set of direct relationship with NOR entry. we are able to see from Figure 3.3.3(B) that counter can take one further clock cycle holdup to alter its state and then it'll work usually till linear unit is de-pronounced and this point in like manner it'll take one clock cycle further to prevent dynamical its state In Figure 3.3.3(C) we've got Affirmed that undesirable yields in sight of Glitches at the linear unit ar avoided. In Figure 3.3.3(E) wave the circumstance once dominant Latch is negative and Counter is what is more negative edge motivated is showed up. The yield of the counter is wrong in lightweight of the manner that it expands once despite once change is turned down as a result of a minor flaw on account of the autumn time holdup of change

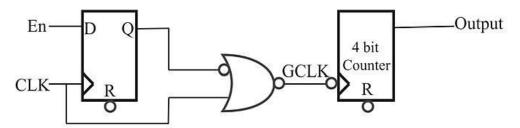

Figure (A):Clock gating of negative edge counter using positive Latch Based NOR gate Circuit.

International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

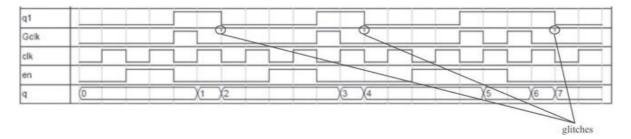

Figure (B): Normal output of negative edge Counter when positive Latch based OR Gated Clock is used.

| q1   |   | _ |  |  |    |  |    |   |

|------|---|---|--|--|----|--|----|---|

| Gclk |   |   |  |  |    |  |    |   |

| clk  |   |   |  |  |    |  |    | l |

| en   |   |   |  |  |    |  |    |   |

| q    | 0 |   |  |  | (1 |  | X2 |   |

Figure (C): Output of negative edge counter when there are some random Hazards at En.

Figure (D): Clock gating of negative edge counter using negative Latch Based NOR gate Circuit.

## III. PROPOSED MODEL

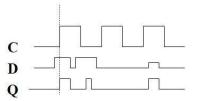

This proposed strategy depends on gathering of FFs which gives combining clock beat. The working of multi-bit D flipflop is like the D head with the exception of that the yield of D Flip Flop takes the condition of the D contribution right now of a positive edge at the clock stick and postpones it by one clock cycle. That is the reason, it is normally known as defer flips flounder. The D Flip-Flop can be deciphered as a defer line or zero request hold. The upside of the D flip-flounder over the D-sort straightforward lock is that the flag on the D input stick is caught the minute the flip-tumble is timed, and resulting changes on the D info will be overlooked until the following clock occasion. From the planning chart in fig 1 plainly the yield Q changes just at the positive edge. At every positive edge the yield Q gets to be distinctly equivalent to the info D right then and there and this estimation of Q is held until the following positive edge.

Figure shows that clock time diagram for clock gating

## International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

# EXPERIMETAL ANALYSIS

| n +• 🗆 # ×                              | 0   | Design Overview     Summary                                                                                            |                             |                                       | ALUB Project Status (07/30 | /2016 - 20:07:29                         | 0           |             |   |

|-----------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|----------------------------|------------------------------------------|-------------|-------------|---|

| ex: 🕐 🎒 Implementation 💿 🚮 Simulation 🚽 | a   | DB Properties     Module Level Utilization     Timing Constraints     Prineut Report     Cock Report     Static Timing | Project File:               | ALU.xise                              | Par                        | er Errors:                               | No Errors   |             |   |

|                                         | 00  |                                                                                                                        | Module Name:                | ALUS                                  | Imp                        | ementation Stat                          | Synthesized |             |   |

| Hierarchy                               |     |                                                                                                                        | Target Device:              | xc6stx100-3fg                         | 2484                       | •Errors:                                 | No Errors   |             |   |

| → ALU                                   |     |                                                                                                                        | Product Version:            | 15E 12-1                              |                            | •Warnings:                               |             | No Warnings |   |

|                                         | -   |                                                                                                                        | Design Goat                 | Balanced                              |                            | Routing Results:     Timing Constraints: |             |             |   |

|                                         | 12  |                                                                                                                        | Design Strategy:            | Xiinx Default (                       | unlocked)                  |                                          |             |             |   |

|                                         | 14  |                                                                                                                        | Environment:                | System Setting                        | 8                          | +Final Timing S                          |             |             |   |

|                                         |     |                                                                                                                        |                             |                                       |                            |                                          |             |             |   |

|                                         |     |                                                                                                                        |                             | Device Utilization Summary (estimated |                            | ated values)                             | d values)   |             |   |

|                                         |     |                                                                                                                        | Logic Utilization           |                                       | Used                       | Available                                | Util        | ization     |   |

| No Processes Running                    |     |                                                                                                                        | Number of Sice LUTs         |                                       | 220                        |                                          | 63288       |             | - |

| Processes: ALU8 - ALU8                  |     |                                                                                                                        | Number of fully used LUT-FF | pairs                                 | 0                          |                                          | 220         |             |   |

| 😑 🎾 ISim Simulator                      |     |                                                                                                                        | Number of bonded IOBs       |                                       | 35                         |                                          | 326         |             | 1 |

| Rehavioral Check Syntax                 |     |                                                                                                                        |                             |                                       |                            |                                          |             |             |   |

|                                         |     |                                                                                                                        |                             |                                       | Detailed Reports           | Reports                                  |             |             | 1 |

|                                         |     |                                                                                                                        | Report Name                 | Status                                | Generated                  | Errors                                   | Warnings    | Infos       |   |

|                                         |     |                                                                                                                        | Synthesis Report            | Current                               | Sat 3, il 30 20:08:30 2016 | 0                                        | 0           | 0           |   |

|                                         |     |                                                                                                                        | Translation Report          |                                       |                            |                                          |             |             |   |

|                                         |     |                                                                                                                        | Map Report                  |                                       |                            |                                          |             |             |   |

| Start 🔍 Design 👌 Files 🚺 Libraries      | 100 | ISE Design Suite InfoCenter                                                                                            | None and Day to Depart      | Design Su                             |                            |                                          | 1           | 1           |   |

| start ut Design Design Design           | -   | ISE Design Suite InfoCenter                                                                                            | <u> </u>                    | Design Su                             | mmary                      |                                          |             |             |   |

| ole.                                    |     |                                                                                                                        |                             |                                       |                            |                                          |             |             |   |

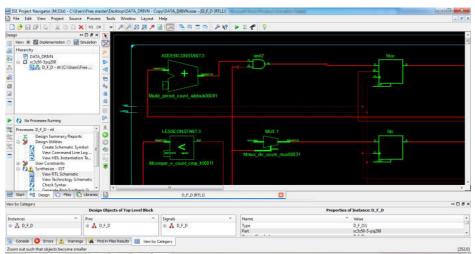

Figure. Show that the starting window of project.

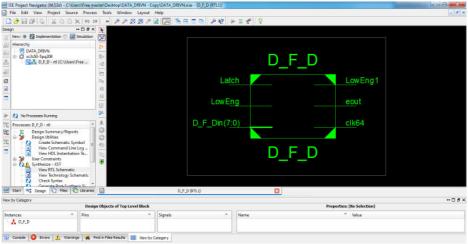

Figure Shows that the parameter being used in a implementation phase will contain the logic gates.

Figure Shows that the implementations phase of D\_F\_D with the logic gates and adder.

## International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

| Des |                                                                                       | 6    | Design Overview                                               |                                                      |                              |                   |                                                              |             |                                                                                                  |  |

|-----|---------------------------------------------------------------------------------------|------|---------------------------------------------------------------|------------------------------------------------------|------------------------------|-------------------|--------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------|--|

| 5   | Ven: 🕦 🌆 Inclementation 🕷 🔜 Simulation<br>Behavioral 🔹                                |      | 108 Properties                                                | Project File:<br>Hodule Name:<br>Target Device:      | ACH2.xise<br>ACH             |                   | arser troors:                                                | No Errorr   | No Errors                                                                                        |  |

|     |                                                                                       |      | Module Level Utilization                                      |                                                      |                              |                   | Implementation State:                                        |             | Placed and Routed                                                                                |  |

|     |                                                                                       |      | Timing Constraints     Pinout Report                          |                                                      | xc3s200-5ft256               |                   | +Errors:                                                     | No Errors   |                                                                                                  |  |

|     |                                                                                       | Ø    | Clock Report                                                  | Product Version:<br>Design Goal:<br>Design Strategy: | ISE 12.1                     |                   | • Warnings:     • Routing Results:     • Timing Constraints: |             | 24 Warmings (24 new)<br>All Samels Completely Routed<br>All Constraints Net<br>© Climing Report) |  |

|     | ACM - rtl (ACM.vhd)                                                                   |      | Errors and Warnings<br>Parser Messages                        |                                                      | Balanced                     |                   |                                                              |             |                                                                                                  |  |

|     |                                                                                       | 18   |                                                               |                                                      | Mine Default Sunlocker       | đ                 |                                                              |             |                                                                                                  |  |

|     |                                                                                       | 26   |                                                               | Environment:                                         | System Settings              |                   | •Final Timing Score                                          | e 0 (Timity |                                                                                                  |  |

|     |                                                                                       |      |                                                               |                                                      |                              |                   |                                                              |             |                                                                                                  |  |

|     |                                                                                       |      |                                                               | [                                                    | - C                          | Device Utilizatio | m Summary                                                    |             |                                                                                                  |  |

| _   | Q The Process Ruring<br>No single design module is selected.<br>⇒ 59 Design Utilities |      | Bitgen Messages                                               | Logic Utilization                                    |                              | Used              | Available                                                    | Utilization | Note(s)                                                                                          |  |

|     |                                                                                       |      | All Implementation Messages                                   | Number of Sice Flip F                                | Plops                        |                   | 143 3,84                                                     | 3%          |                                                                                                  |  |

|     |                                                                                       |      | Ortailed Reports     Synthesis Report     Transfittion Damage | Number of #input LU                                  |                              | -                 | 268 3,84                                                     | 6%          |                                                                                                  |  |

| 1   |                                                                                       |      |                                                               | Number of occupied 5                                 | Slices                       |                   | 210 1,92                                                     | 10%         |                                                                                                  |  |

| 121 |                                                                                       |      | Design Properties<br>Enable Message Filtering                 | Number of Slices of                                  | ontaining only related logic |                   | 210 210                                                      | 1 100%      | 1                                                                                                |  |

|     |                                                                                       |      | Optional Design Summary Contents                              | Number of Sices of                                   | ontaining unrelated logic    | 1                 | 0 210                                                        | 0%          |                                                                                                  |  |

|     |                                                                                       |      | Show Clock Report                                             | Total Number of 4 inp                                | NUT LIUTS                    | 1                 | 402 3,84                                                     | 10%         |                                                                                                  |  |

|     |                                                                                       |      | Show Feiling Constraints<br>Show Wernings                     | Number used as lo                                    | gic                          |                   | 268                                                          |             |                                                                                                  |  |

|     |                                                                                       |      | Show Errors                                                   | Number used as a route-thru Number of bonded 100s    |                              |                   | 134                                                          |             |                                                                                                  |  |

|     |                                                                                       |      |                                                               |                                                      |                              |                   | 13 17                                                        | 3 7%        |                                                                                                  |  |

|     |                                                                                       |      |                                                               | Number of BUFGMUXs                                   |                              |                   | 2                                                            | 3 25%       |                                                                                                  |  |

|     | Start 🕫 Design 🚺 Files 🚺 Libraries                                                    | x    | Design Su                                                     | mmary                                                |                              |                   |                                                              |             |                                                                                                  |  |

| h   | v by Cabegory                                                                         |      |                                                               |                                                      |                              |                   |                                                              |             |                                                                                                  |  |

|     | Design                                                                                | 0bje | cts of Top Level Block                                        |                                                      |                              |                   | Properties: (No Sel                                          | action)     |                                                                                                  |  |

|     | tances + Pins                                                                         |      | <ul> <li>Signals</li> </ul>                                   | *                                                    | Name                         |                   | * Value                                                      |             |                                                                                                  |  |

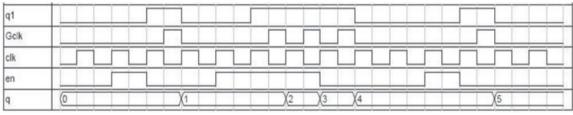

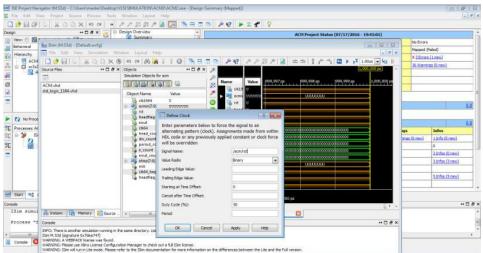

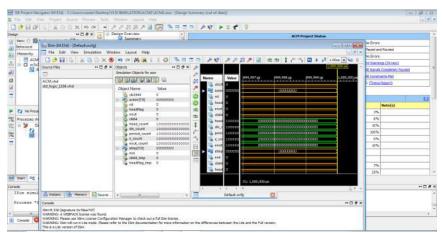

Figure Shows that the all implementation parameter values used in implementation phase with logic utilization value and number of flip flop values.

Figure Shows that the all initially implementation parameter values for the DFD 2 files used in implementation phase with logic utilization value and number of flip flop values.

Figure Shows that the all implementation parameter values for the DFD 2 files used in implementation phase with logic utilization value and number of flip flop values.

#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

## IV. COMPARATIVE RESULT ANALYSIS

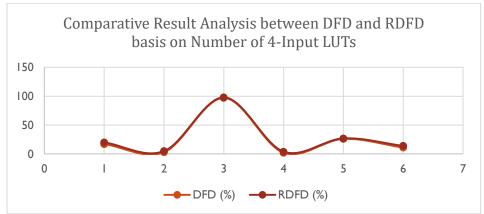

Figure : shows that comprative result analysis of Number of Occupied Files, Number of Slices Containing Only Related Logic, Number of Slices Containing Only Unrelated Logic, Total Number Of 4 input LUTS, Number of Bonded on the basis of Number of 4-Input LUTs and clock edge data (1110) for DFD, RDFD, Used, Available and Utilization in Logic Circuit.

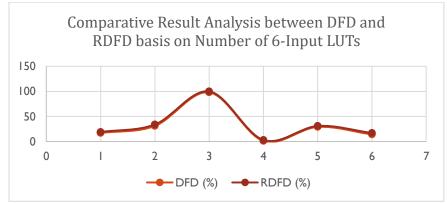

Figure : shows that comprative result analysis of Number of Occupied Files, Number of Slices Containing Only Related Logic, Number of Slices Containing Only Unrelated Logic, Total Number Of 4input LUTS, Number of Bonded on the basis of Number of 6-Input LUTs and clock edge data (1101) for DFD, RDFD, Used, Available and Utilization in Logic Circuit.

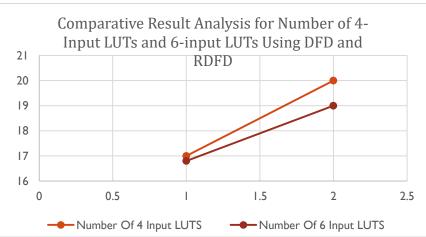

Figure: shows that comprative result analysis between DFD and RDFD forNumber of 4-Input LUTs and Number of 6-Input LUTs in Logic Circuit.

#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 8, Issue 11, November 2019

### V. CONCLUSION

Our proposed procedure decreases the planner's trouble for investigating all the flip-flops for meeting the planning prerequisites. Information driven clock, sidestep no-account of same planning requirements so that a great part of the planning way which rehashed to the single information driven decreases figuring. A portion of the default parameter of VLSI, for example, default counterbalance after out for clock, default period examination is most presumably settled and those are not having much variety. The graphical representation for looking at flip-slump depends on gathering amongst existing and proposed strategies. The principal bar speaks to the flip-slump number of gathering utilizing existing systems and the second bar speaks to the flip-tumble tally of gathering utilizing proposed strategies. In present VLSI plan territory is one of the critical issues to be tended. To accomplish lessened territory different sorts of flip slumps and move enlist are talked about. Single piece flip tumble and Multi bit flip slump are actualized to accomplish less use of zone. Different size of move enroll is executed with gathering of flip flounder. This proposed strategy is executed in Xilinx Virtex 5 VLSI family. Exploratory outcomes are focused to number of flip flounder use, deferral and clock cradle. Flip tumble range use is minimized around to half. Along these lines this proposed strategy is more appropriate for lessening of equipment.

#### REFERENCES

- [1]. Shmuelwimer And Israel Koren "Design Flow For Flip-Flop Grouping In Data-Driven Clock Gating", Ieee, 2014, Pp 771-778.

- [2]. A. Rangana Yakulu And K. Satya Prasad "Low Power Correlator Using Signal Range And Sub Word Based Clock Gating Scheme", International Journal Of Hybrid Information Technology, 2016, Pp 159-170.

- [3]. T.Naresh And M.Lakshmikiran "Power Reduction With Flip Flop Grouping In Data Driven Clock Gating", International Journal Of Engineering And Computer Science, 2015, Pp 11835-11838.

- [4]. Dushyant Kumar Soni And Ashishhiradhar "Dynamic Power Reduction Of Synchronous Digital Design By Using Of Efficient Clock Gating Technique", International Journal Of Engineering And Techniques, 2015, Pp 18-23.

- [5]. Vidya K And Mr R. Karthik "A Look Ahead Partial Bus Specific Clock Gating Based On Autogated Flipflops", International Journal Of Research In Science And Engineering, 2015, Pp 1-7.

- [6]. Saurabhkshirsagar And Dr. M B Mali "Data Driven Clock Gating For Logical Groups In Low Power Applications", Ijesc, 2015, Pp 1454-1457.

- [7]. Renukajaiswal, Ranbir Paul And Vikasranjanmahto "Power Reduction In Cmos Technology By Using Tri-State Buffer And Clock Gating", Ijarcet, 2014, Pp 1853-1860.

- [8]. R Dhivyabharathi & M Sunil Karthik "A Pass Transistor Based D Flip-Flop Design Using Negative Edge Triggered Circuit", Ijerst, 2015, Pp 63-69.

- [9]. S Chindhu And S Thenappan "Pass Transistor Based Conventional Data Flip Flop Design", Ijerst, 2015, Pp 278-284.

- [10]. Kakarlasandhya Rani And Krishna Prasad Satamraju "A Novel Approach For Auto Clock Gating Of Flip-Flops", Ijser, 2015, Pp 132-136.

- [11]. Anujaaravind And Raseena K.A "Design Of An Alu With A Low Power Lfsr Using Clock Gating", Ijsetr, 2014, Pp 2636-2639.

- [12]. Abhishekmashetty, Rajashekar Reddy Merugu, Sanjay Dubey And Vejandla Vijay Bhaskar "Data Driven Clock Gating Technique For Dynamic Power Reduction In Digital Design", Journal Of Chemical And Pharmaceutical Sciences, 2016, Pp 511-514.

- [13]. C.Subin Raj, S.Jebasingkirubakaran And P.Balavengateswarlu "Look Ahead Clock Gating Using An Auto Gated Flip Flop For Low Power Application", Journal Of Chemical And Pharmaceutical Sciences, 2016, Pp 969-973.

- [14]. D.Nirosha And T.Thangam "Design And Implementation Of 32 Bit Alu Using Look Ahead Clock Gating Logic", Ijeter, 2016, Pp 101-104.

- [15]. Shmuelwimer And Aryealbahari "A Look-Ahead Clock Gating Based On Auto-Gated Flip-Flops", Ieee, 2014, Pp 1465-1472.

- [16]. Mayuri B. Junghare & Aparna S. Shinde "A clock gating technique using auto gated flip flop for look ahead clock gating", Ijsr, 2013, Pp 1525-1530

- [17]. Zhengxu And Kenneth L. Shepard "Design And Analysis Of Actively-Deskewed Resonant Clock Networks", IEEE, 2009, Pp 558-568.

- [18]. Jason H. Anderson And Farid N. "Power Estimation Techniques For Fpgas", Ieee, 2004, Pp 1015-1027.

- [19]. D.Popa, Z.Sun, F.Torrisi, T.Hasan, F.Wang & A.C.Ferrari "Sub 200fs pulse generation from a graphene mode-locked fiber laser", IEEE 2010, Pp1-3 [20]. Wimbogaerts, Shankar Kumar Selvaraja, Pieter Dumon, Joostbrouckaert, Katrien De Vos, Dries Van Thourhout And Roelbaets "Silicon-On-

- Insulator Spectral Filters Fabricated With Cmos Technology", Ieee, 2010, Pp 33-44.

- [21]. Shmuel Wimer And Arye Albahari "A Look-Ahead Clock Gating Based On Auto-Gated Flip-Flops", Ieee, 2014, Pp 1465-1475.