Vol. 9, Issue 2, February 2020

# Comparative Analysis and Behavior of Digital Applications simulated using MOSFET, CNTFET and FinFET Transistors in HSPICE

# Malti Bansal<sup>1</sup>, Harsh Saxena<sup>2</sup>

Department of Electronics & Communication Engineering, Delhi Technological University, Delhi-110042, India<sup>1,2</sup>

**Abstract:** Full Adder constitutes elementary building block for advanced digital applications. SRAM is a runtime memory unit which performs fast read and write operations. These digital applications dissipate considerable power when synthesized using MOS. FinFET and CNTFET implementations of these circuits have improved power dissipation, delay & scalability characteristics over MOSFET, The HSPICE tool by Synopses designs logical and arithmetic applications and analyse power delay behavior. Library files for coding of FinFET are provided by BSIM & for CNTFET are provided by Stanford Library. Input /Output waveforms have been provided for both applications.

Keywords: FinFET, Nano tubes, CNTFET, SRAM, Full Adders

## I. INTRODUCTION

As the miniaturization reached nanometer level with the increasing need of compact faster processing circuits, shrunken MOSFETs suffer from reliability problems because of excessive heating. The thin body MOSFET is the backbone of FinFET. Scaled MOSFET channel length when reduced below a critical value decreased the gate control over the channel. Also increases the power dissipation. As per the structure, FinFET is a double gate MOSFET, to control the channel and offers distinct advantages for scaling into very short gate lengths. The two gates together strongly influence the channel potential, combating the drain impact, and leading to the better ability to shut off the channel current, reducing Drain Induced Barrier Lowering (DIBL). The Short Channel Effect (SCE) can be suppressed and the power dissipation can be reduced by decreasing the fin width (Tfin). This is reported by P.C.Rajashree et al[1].

'CNTFET' uses 'CNT' as their semiconducting channels. A 'Single-Wall CNT' (SWCNT) made up of one cylinder only. This makes fabrication of these device easier Assessment of performance begins with the analysis in basic or simple circuit blockshence they are first implemented in Full Adder which forms the basis of arithematic electronics. Full adder implementation is followed by SRAM cell analysis when implemented with MOS and FinFET.

## **II. SIMULATION TOOL**

'SPICE' stands for "Simulation Program with Integrated Circuits Emphasis". It's a powerful tool with innumerous libraries to simulate electrical circuits. From the steady-state, transient, to frequency domains all the analysis can be done easily. Its Netlist file contains the node configuration. The file has '.SP extension'. Secondly the model files are there in Netlist. The transistor, diode etc electronic component implementation using MOS, FinFET are there in model files of the simulator as mentioned in K.Skundert et al[3].The netlist code is then browsed and added to "HSPUI" (HSPICE User Interface).Finally the Waveforms are provided by the Avanwaves feature of HSPICE

| File Co         | nfiguration To                                  | ol Help   |         |            |            |     |

|-----------------|-------------------------------------------------|-----------|---------|------------|------------|-----|

| Design<br>Title | c:\users\harsh\desktop\major2\mos\full adder.sp |           |         |            |            |     |

| Listing         | c:\users\hars<br>C:\synopsys\                   | Hspice_A- |         | hspice.exe |            |     |

|                 | ☐ Start C/S n                                   | 0000      | 1 one c | 13 10000   |            |     |

| Open            | Start C/S n                                     | Edit NL   | Edt St  | Explore    | Multi-jobs | Ext |

Fig (i) HSPICE user interface from Synopses(hspui)

Vol. 9, Issue 2, February 2020

# **III. DIGITAL APPLICATIONS**

# A) Full Adder

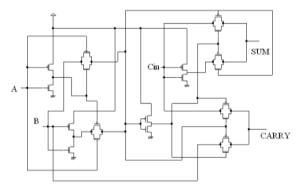

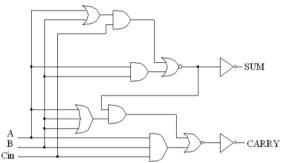

The basic gates SOP and POS equation of full adder cannot be reduced using KMAP however full adder can be implemented using CMOS technology to reduce the gate count, delay in output etc. Few logical tricks are carried out to decrease the transistor count like utilizing partial output of sum for carry – generation circuits. However, this increases delay. Further studies led to the implementation of carry look ahead generator but then circuit complexity increased [2]. The figure(ii) shows the complementary static CMOS implementation of full adder, and the corresponding gate level implementation is shown in figure (iii). It requires 28 transistors. In addition to consuming a large area, this circuit is slow. We are using 28 transistor logics in our project.

Fig. (ii) Full adder circuit implemented using Twenty Eight transistors in complementary configuration

Fig (iii) Gate level implementation of Full adder designed using Twenty Eight CMOS Transistors

| Transistor          | Time Delay (sec)         | Power Dissipation(W)                   |  |

|---------------------|--------------------------|----------------------------------------|--|

| MOSFET              | 9.368x 10 <sup>-8</sup>  | 1.06 x 10 <sup>-6</sup>                |  |

| FinFET              | 9.87 x 10 <sup>-9</sup>  | 1.909 x 10 <sup>-7</sup>               |  |

| CNTFET              | 9.979 x 10 <sup>-9</sup> | 3.059 x 10 <sup>-7</sup>               |  |

|                     |                          |                                        |  |

| [a] 500m            |                          |                                        |  |

| 1411 3500 a         |                          |                                        |  |

| [4] 500m            |                          |                                        |  |

| 500m                |                          |                                        |  |

| 1<br>1<br>500n<br>6 |                          |                                        |  |

|                     | 50n 100n                 | 150n 200n 250n 31<br>Time (ini) (TIME) |  |

Table 1:Comparision of Performance (Full Adder)

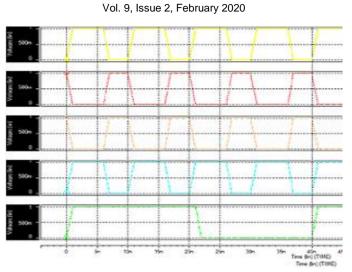

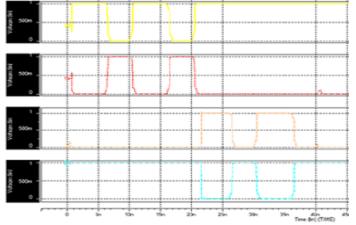

Fig.(iv) Input and output waveforms obtained using Avanwaves for the full adder design

| Table 2: I/O parameters for Fig.(iv) |             |              |  |

|--------------------------------------|-------------|--------------|--|

| Symbol                               | Graph Color | Description  |  |

| V(2)                                 | Yellow      | First Input  |  |

| V(3)                                 | Red         | Second Input |  |

| V(4)                                 | Brown       | Carry Input  |  |

| V(10)                                | Light Blue  | Carry Output |  |

| V(18)                                | Green       | Sum          |  |

Vol. 9, Issue 2, February 2020

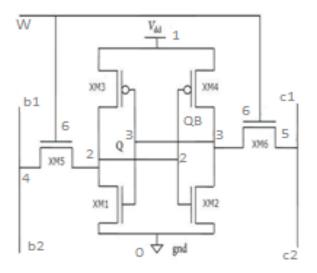

## b) 2 X 2 SRAM Memory

SRAM has exhaustive implementation as temporary storage in computer which speeds its operations. The 2 X 2 SRAM Memory consists of two memory words, each having a size of two bits. Every bit is stored in a six transistor SRAM cell, working in two possible modes: Read and Write. Our prime focus in this project is to perform Write operation. The necessity condition for sustaining an SRAM cell is Strength(W/L) of Pull up Transistor(XM3,XM4) << Strength of Access Transistor(XM5,XM6) << Strength of Pull down Transistors(XM1,XM2). For the Write operation to write '0' Word line(W) should be high, bit line (b1/b2) =1, complementary bitline(c1/c2))=0. Later when word line(W) is low, the bit '0' stored in cell will be preserved at node Q[2]. This is depicted combinedly by fig (vi) and fig (iv). Here X1-X4 are the SRAM cells of fig (v). This is reported by Ravi Kumar et al[7]

Fig.(v) 2 X 2 SRAM MEMORY UNIT

Fig.(vi) A bistable cross coupled SRAM using 6 Transistors

| Transistor | Time Delay                | Power Dissipation         |

|------------|---------------------------|---------------------------|

| MOSFET     | 2.1888 x 10 <sup>-8</sup> | 4.707 x 10 <sup>-5</sup>  |

| FinFET     | 4.4163 x 10 <sup>-9</sup> | 4.7376 x 10 <sup>-6</sup> |

Fig. (vii) Input waveform obtained using Avanwaves for 2X2 SRAM Memory unit

Fig. (viii) Output Waveformfrom Avanwavefor 2X2 SRAM Memory unit

| Table 4: Relevent data for fig (vii) |                    |                                                |  |  |

|--------------------------------------|--------------------|------------------------------------------------|--|--|

| Symb.                                | <b>Graph Color</b> | Description                                    |  |  |

| V(b1)                                | Yellow             | Read Input to the First bit [BL]               |  |  |

| V(c1)                                | Red                | Complementry Read Input to the First bit [BLB] |  |  |

| V(b2)                                | Orange             | Read Input to the Second bit [BL]              |  |  |

| V(c2)                                | Blue               | Complementry Read Input to the Second bit      |  |  |

| V(w)                                 | Green              | Write Input to the First word(X1,X2) [WL]      |  |  |

| Table5: Important | information f | for fig. (viii) |

|-------------------|---------------|-----------------|

|-------------------|---------------|-----------------|

| Symbol | <b>Graph Color</b> | Description        |

|--------|--------------------|--------------------|

| V(q1)  | Yellow             | Data written in X1 |

| V(q0)  | Red                | Data written in X2 |

| V(p1)  | Brown              | Data written in X3 |

| V(p0)  | Blue               | Data written in X4 |

## **IV. CONCLUSION**

The results read aloud that FinFET and CNFET Full adder circuits have faster response than their MOSFET counterpart. However FinFET and CNTFET circuits have nearly same response speed. Also Power dissipation of FinFET adder is five times lesser than MOSFET implementation and is little below CNTFET implementation. Power dissipation in MOSFET based SRAM array is almost Ten times its FinFET counterpart. FinFET response is faster with delay in picoseconds. The delay in the MOS based SRAM is almost Ten times.

Vol. 9, Issue 2, February 2020

## REFERENCES

- [1]. "Deep Submicron" 50nm CMOS Logic Design With FINFET P.C.Rajashree, Ancy Thomas, Rose Jaria, Jane Precilla, Alfred Kirubaraj Department Of ECE, Karunya University, Coimbatore, Tamil Nadu, India

- [2]. http://shodhganga.inflibnet.ac.in/bitstream/10603/6521/9/09\_chapter%204.pdf

- [3]. "K. S. Kundert", The Designer's Guide to SPICE and Spectre, Kluwer. Academic Publishers, Boston , 1995

- [4]. Dragica Vasileska; Stephen Goodnick (2006). Computational Electronics. Morgan & Claypool.p. 103. ISBN 1-59829-056-8.

- [5]. "Frontier Semiconductor Paper" (PDF). Archived from the original (PDF) on February 27, 2012. Retrieved 2012-06-02.

- [6]. Wai-Kai Chen (2006). The VLSI Handbook.CRC Press. Fig. 2.28, p. 2–22. ISBN 0-8493-4199-X.

- [7]. Ravi Kumar. K. I, Vijayalaxmi. C. Kalal, Rajani. H. P, Dr. S. Y.Kulkarni "Design and Verification of Low Power 64bit SRAM System using 8T SRAM:Back-End Approach"

- [8]. W. Zhang, J. G. Fossum, L. Mathew, and Y. Du, "Physical insights regarding design and performance of independent-gate FinFETs," IEEE Trans. Electron Devices, vol. 52, no. 10, pp. 2198–2206, Oct. 2005.

- [9]. P. Mishra and N.K. Jha, "Low-power FinFET circuit synthesis using surface orientationoptimization," in Proc. Design Automation and Test in Europe, Mar. 2010, pp. 311

- [10]. A. Muttreja, N. Agarwal, and N.K. Jha, "CMOS logic design with independent gate FinFETs," in Proc. Int. Conf. Computer Design, Oct. 2007, pp. 560-567.

- [11]. M. Shrivastava, M. Agrawal, J. Aghassi, H. Gossner, W. Molzer, T. Schulz, and V. R. Rao, "On the thermal failure in nanoscale devices: Insight towards heat transport including critical BEOL and design guidelines for robust thermal management & EOS/ESD reliability," in Proc.Int. Reliab. Phys. Symp., pp. 3F.3.1–3F.3.5, 2011.

- [12]. L. Zhang, J. He, F. Liu, J. Zhang, Y. Song, "A Unified charge-based model for symmetric DG MOSFETs Valid for both heavily doped body and undoped Channel," International conference on Mixed Design of Integrated Circuits and Systems (MIXDES 2008), June 2 1- 23 pp.367-372, Poland, 2010.

- [13]. Lin, Yu-Ming; Tsang, James C; Freitag, Marcus; Avouris, Phaedon (2007). "Impact of oxide substrate on electrical and optical properties of carbon nanotube devices