#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9. Issue 3. March 2020

# Gate Clock Loop Pipelining of Binary Instruction Traces Power Reduced as A Review

## Ateek Mansoori<sup>1</sup>, Dr. Bharti Chourasia<sup>2</sup>

PG Student [Digital Communication], Dept. of ECE, R.K.D.F. Institute of Science & Technology Bhopal (M.P.)<sup>1</sup>

Associate Professor & HOD of ECE, R.K.D.F. Institute of Science & Technology Bhopal (M.P.)<sup>2</sup>

**Abstract:** The increasing demand for low power mobile computing and consumer electronics products has refocused VLSI design in the last two decades on lowering power and increasing energy efficiency. Power reduction is treated at all design levels of VLSI chips. From the architecture through block and logic levels, down to gate level circuit and physical implementation, one of the major dynamic power consumers in the system clock signal, typically responsible for up to 50% of the total dynamic power consumption. Clock network design is a delicate procedure and is therefore done in a very conservative manner under worst case assumptions. It incorporates many diverse aspects such as selection of sequential elements, controlling the clock skew, the decision of the topology and physical implementation of the clock distribution network.

**Keywords:** Data Driven, Logic Gates, Flip-Flops, Clock Gating, AND Clock Gating, NOR Clock Gating, Latch based Clock Gating.

#### **I.INTRODUCTION**

A data driven clock with inspected wellsprings of information may be useful in a circumstance where an IP square may increase forward ground paying little notice to the amount of information sources that are readied. One instance of such a square may be a secretly checked switch in an on-chip compose. In the revelation of a data port request drives a decision to be made on

Whether to yield data from each data port on the accompanying clock cycle. By virtue of an on-chip switch additional clock cycles would should be delivered to guarantee bundles upheld inside the switch increased forward ground when no new data was pending.

#### 1.1 CLOCK GATING

They portrayed a couple of methods to diminish the dynamic power are created, of which clock gating is ruling. As a rule, when a method of reasoning unit is planned, its essential progressive parts get the clock signal, paying little notice to paying little aware to whether they will flip in the accompanying cycle. With clock gating, the clock signs are AND with unequivocally pre-described enabling signs. Time gating is used at all levels: Structure Designing, Square Blueprint, Method of reasoning arrangement, and door. A couple of procedures to endeavor this system are depicted, with each one of them relying upon various heuristics attempting to grow clock gating openings.

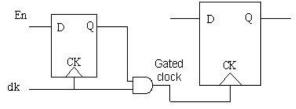

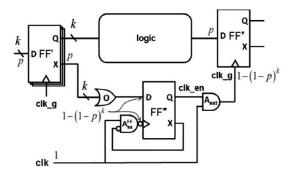

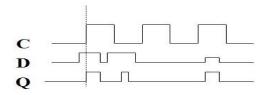

Figure: Clock Gating

## AUTO GATED FLIP-FLOP

Flip-flops have their substance replace either at the up or down edge of the alter flag. In any situations, once the up or down edge of the change hail, the flip-flops substance stays steady paying little heed to the path that the data replace. Inan especially standard D Flip-Flop, the clock signal fix streams into the D flip-Flop paying little mind to regardless of whether

#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9. Issue 3. March 2020

the data replaces or not. The clock parts essentialness is eaten up by within clock support to manage the transmission portals senselessly. Thus, if the commitment of the flip-struggle is the photo of its yield, the move of the clock will be smothered to direct power.

**II.LITERATURE SURVEY**

It is focusing on various types of fractal geometry antenna uses for multiband

Homayoon Oraizi and Shahram Hedayati Shmue Wimer, Israel Koren "Outline Flow for Flip-Flop Grouping in Data-Driven Clock Gating" According to examiner, Clock gating is an otherworldly methodology used for power saving. It is watched that the customarily used union based gating still leaves a considerable measure of monotonous clock beats. Data driven gating expects to weaken these. To reduce the hardware overhead included, flip-flops (FFs) are collected so they share an ordinary clock enabling sign. Ranganayakulu and K. Satyaprasad "Low Power Correlated Using Signal Range and Sub Word Based Clock Gating Scheme", International Journal of Hybrid Information Technology,

They discussed look into work presents novel sub word allotted banner run based clock gating technique, which can be to a great degree successful in banner planning applications. A flexible VHDL model is created for the Correlator outline with the proposed clock gating arrangement. MATLAB script made test data is used for valuable affirmation. Xilinx FPGA based union and power examination instruments are used to analyze the power improvement of proposed building.

T.Naresh and M.LakshmiKiran "Control Reduction with FlipFlop Grouping in Data Driven Clock Gating",

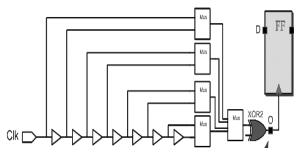

They discussed the overabundance check beats in a high repeat clock banner are discarded by performing AND operation on Enable banner and associated clock signal. Enable banner is controlled by performing XOR operation on data and yield of back to back part, for instance, Flip flop. ANDed yield—the Gated clock signal serves as clock to the present circuit, which contains time heartbeats at the trading activities of information banner. This procedure can be contacted assembling of Flip-disappointments having nearly trading commitments by performing OR operation on the enable indications of all Flip flops in the social occasion

Dushyant Kumar Soni and Ashish Hiradhar "Dynamic Power diminishment of synchronous computerized configuration by utilizing of proficient clock gating strategy"

They present a relative examination of existing clock gating procedures on some synchronous moved plot like ALU (Arithmetic Logic unit) and so on. Another clock gating philosophy that gives more invulnerability to the present issue in available strategy . In new discussed clock gating the Gated Clock Generation Circuit is using tri state support and Gated basis is used which is made by the blend of twofold gated (AND, OR, AND method of reasoning entryway) with permeated input independently

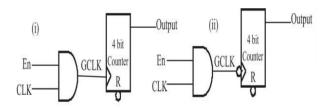

Vidya K and Mr R. Karthik "A LOOK AHEAD PARTIAL BUS SPECIFIC CLOCK GATING BASED ON AUTOGATED FLIPFLOPS"

They introduced, the auto gated flip-flops which are to use clock gating technology for simply little power use. The using clock beats for the gathered planning signs to the gated justification. The look ahead technique can same to topic the deferral and the mutilations from the circuit for the achievement of the application stage.

Saurabh Kshirsagar and Dr. M B Mali "Information Driven Clock Gating for Logical Groups in Low Power Applications", They portray VLSI and diverse equipment wanders has ended up being quick drawing closer to address the three astoundingly fundamental problems size, power and speed. As demonstrated by maker, the issue of component power dispersal is tended]

#### III.PROBLEM IDENTIFICATION

The use of force is significant issue in outline of computerized circuit for complex equipment with the end goal of portable correspondence and another imparting gadget. For the decrease of force utilization utilized clock gating framework. The clock gating framework lessens the utilization of force approx. (10-19%). Presently a day utilized different clock gating

#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9, Issue 3, March 2020

framework, for example, AND, NOR and hook based clock gating framework. A few procedures to lessen the dynamic power are created, of which clock gating is dominating. Commonly, when a rationale unit is timed, its fundamental successive components get the clock flag, paying little respect to regardless of whether they will flip in the following cycle. With clock gating, the clock signs are ANDed with unequivocally pre-characterized empowering signals. Time gating is utilized at all levels: framework engineering, square outline, rationale plan, and doors [2,3]. A few strategies to exploit this procedure are portrayed in [4,6] with every one of them depending on different heuristics trying to expand clock gating openings. Another gathering of FFs for clock exchanging power lessening, called multi-bit FF (MBFF).

The FFs' format vicinity some basic issue characterizes identified with configuration issue of hook based clock gating framework

- 1. Selection of group of FFs

- 2. Proper selection of Algorithm

- 3. Backend design of flow

- 4. Distribution of clock network

- 5. Maximum diameter of FFs group

This information driven clock gating causes territory and power overhead. The power utilization could be lessened by utilizing clock gating procedure. This information driven bolt gating signals having action to empower the clock signals. In this way, the flip lemon and also the locks square measure to be sceptered by utilizing the door signals. The yields from the XOR entryways square measure ORed to relinquish the combo of yield joint door signals from the flip tumbles and after that locked to stay away from the glitches exhibited in the predetermined units. The clock of the flip slump can be disabled within the concomitant cycle by XORing.

its yield with the current knowledge that may seem at its yield within the following cycle. the data driven gating experiences a brief timeframe window where the gating hardware can appropriately work.

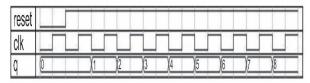

**AND CLOCK GATING** In successive circuit one two-information AND entrance is put in in methodology of reasoning for clock gating. One commitment to AND approach is check memory the second knowledge could be a banner accustomed management the yield (suggests it'll management the rear to back circuit's clock). For experimental reason we have a tendency to square measure taking a vital counter showed up in Figure. Basic Counter(negative edge triggered).

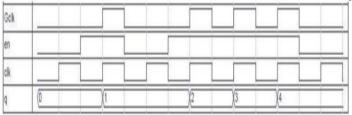

Figure (A): Normal output of the counter without Clock Gating.

Figure (B):Clock gating using AND gate Circuit.

#### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9. Issue 3. March 2020

Figure (B): Output of Counter when Counteris Negative edge triggered.

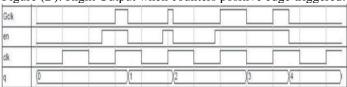

Figure (C): Wrong Output due to Glitch, when counters Positive edge triggered.

Figure (D): Right Output when counters positive edge triggered.

Figure (E): Hazards Problem when AND clock gating Circuitry used.

#### V.PROPOSED MODEL

This proposed strategy depends on gathering of FFs which gavottes combining clock beat. The working of multi-bit D flip-flop is like the D head with the exception of that the yield of D Flip Flop takes the condition of the D contribution right now of a positive edge at the clock stick and postpones it by one clock cycle. That is the reason, it is normally known as defer flips flounder. The D Flip-Flop can be deciphered as a defer line or zero request hold. The upside of the D flip-flounder over the D-sort straightforward lock is that the flag on the D input stick is caught the minute the flip-tumble is timed, and resulting changes on the D info will be overlooked until the following clock occasion. From the planning chart in fig 1 plainly the yield Q changes just at the positive edge. At every positive edge the yield Q gets to be distinctly equivalent to the info D right then and there and this estimation of Q is held until the following positive edge.

## International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9, Issue 3, March 2020

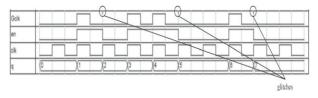

Figure shows that clock time diagram for clock gating

Information driven Flip Flop which takes various information info and results in numerous information yield. The working of multi-bit flip flounder is same as single-piece flip slump, at whatever point the clock gets dynamic state flip tumble hooks all contribution to yield. For latent express the flip flounder holds the information. The fundamental structure of information driven flip slump is given in figure 3.4.2 and its relating waveform is given in figure In present VLSI plan territory is one of the critical issues to be tended. To accomplish lessened territory different sorts of flip slumps and move enlist are talked about. Single piece flip tumble and Multi bit flip slump are actualized to accomplish less use of zone. Different size of move enroll is executed with gathering of flip flounder.

#### **Problem Identification and Formulation**

Common problem defines related to design issue of latch based clock gating system Selection of group of FFs Proper selection of Algorithm Distribution of clock network. The design and simulation of proposed model of clock gating for grouping of FFs architecture for the processing of reduction of power consumption. The design data driven simulate in Xilinx.

#### **VI.CONCLUSION**

This proposed strategy is executed in Xilinx Virtex 5 VLSI family. Exploratory outcomes are focused to number of flip flounder use, deferral and clock cradle. Flip tumble range use is minimized around to half. Along these lines this proposed strategy is more appropriate for lessening of equipment.

#### VII.SUGGESTIONS FOR FUTURE WORK

The outline of information driven clock gating framework utilizing AND or NOR with the mix of Latch based clock gating framework. The clock gating framework utilized BAN arrange for clock dissemination and decreases the utilization of force. In future utilized lower level clock gated contribution for enhancement of force.

#### REFERENCES

- [1]. Shmuel Wimer and Israel Koren "Design Flow for Flip-Flop Grouping in Data-Driven Clock Gating", IEEE, 2014, Pp 771-778.

- [2]. A. Rangana yakulu and K. Satya prasad "Low Power Correlator Using Signal Range and Sub Word Based Clock Gating Scheme", International Journal of Hybrid Information Technology, 2016, Pp 159-170.

- [3]. T.Naresh and M.LakshmiKiran "Power Reduction with Flip Flop Grouping in Data Driven Clock Gating", International Journal Of Engineering And Computer Science, 2015, Pp 11835-11838.

- [4]. Dushyant Kumar Soni and AshishHiradhar "Dynamic Power reduction of synchronous digital design by using of efficient clock gating technique", International Journal of Engineering and Techniques, 2015, Pp 18-23.

- [5]. Vidya K and Mr R. Karthik "A LOOK AHEAD PARTIAL BUS SPECIFIC CLOCK GATING BASED ON AUTOGATED FLIPFLOPS", International Journal of Research in Science and Engineering, 2015, Pp 1-7.

- [6]. SaurabhKshirsagar and Dr. M B Mali "Data Driven Clock Gating for Logical Groups in Low Power Applications", IJESC, 2015, Pp 1454-1457.

- [7]. RenukaJaiswal, Ranbir Paul and VikasRanjanMahto "Power Reduction in CMOS Technology by using Tri-State Buffer and Clock Gating", IJARCET, 2014, Pp 1853-1860.

- [8]. R DhivyaBharathi and M Sunil Karthik "A PASS TRANSISTOR BASED D FLIP-FLOP DESIGN USING NEGATIVE EDGE TRIGGERED CIRCUIT", IJERST, 2015, Pp 63-69.

- [9]. S Chindhu and S Thenappan "PASS TRANSISTOR BASED CONVENTIONAL DATA FLIP FLOP DESIGN", IJERST, 2015, Pp 278-284.

- [10]. KakarlaSandhya Rani and Krishna Prasad Satamraju "A Novel Approach for Auto Clock Gating of Flip-Flops", IJSER, 2015, Pp 132-136.

- [11]. AnujaAravind and Raseena K.A "Design of an ALU with a low power LFSR using Clock gating", IJSETR, 2014, Pp 2636-2639.

- [12]. AbhishekMashetty, Rajashekar Reddy Merugu, Sanjay Dubey and Vejandla Vijay Bhaskar "Data driven clock gating technique for dynamic power reduction in digital design", Journal of Chemical and Pharmaceutical Sciences, 2016, Pp 511-514.

- [13]. C.Subin Raj, S.JebasingKirubakaran and P.BalaVengateswarlu "Look Ahead Clock gating using an Auto gated Flip flop for Low Power Application", Journal of Chemical and Pharmaceutical Sciences, 2016, Pp 969-973.

- [14]. D.Nirosha and T.Thangam "Design and Implementation of 32 Bit ALU Using Look Ahead Clock Gating Logic", IJETER, 2016, Pp 101-104.

- [15]. ShmuelWimer and AryeAlbahari "A Look-Ahead Clock Gating Based on Auto-Gated Flip-Flops", IEEE, 2014, Pp 1465-1472.

ISSN (Online) 2278-1021 ISSN (Print) 2319-5940

### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 9, Issue 3, March 2020

- [16]. Mayuri B. Junghare and Aparna S. Shinde "A Clock Gating Technique Using Auto Gated Flip Flop for Look Ahead Clock Gating", IJSR, 2013, Pp 1525-1530.

- [17]. ZhengXu and Kenneth L. Shepard "Design and Analysis of Actively-Deskewed Resonant Clock Networks", IEEE, 2009, Pp 558-568.

- [18]. Jason H. Anderson and Farid N. "Power Estimation Techniques for FPGAs", IEEE, 2004, Pp 1015-1027.

- [19]. D. Popa, Z. Sun, F. Torrisi, T. Hasan, F. Wang and A. C. Ferrari "Sub 200fs pulse generation from a graphene mode-locked fiber laser", IEEE, 2010, Pp 1-3.

- [20]. WimBogaerts, Shankar Kumar Selvaraja, Pieter Dumon, JoostBrouckaert, Katrien De Vos, Dries Van Thourhout and RoelBaets "Silicon-on-Insulator Spectral Filters Fabricated With CMOS Technology", IEEE, 2010, Pp 33-44.

- [21]. Shmuel Wimer and Arye Albahari "A Look-Ahead Clock Gating Based on Auto-Gated Flip-Flops", IEEE, 2014, Pp 1465-1475.