221

International Journal of Advanced Research in Computer and Communication Engineering

Vol. 10, Issue 12, December 2021 DOI: 10.17148/IJARCCE.2021.101243

# Design Implementation of SRAM cell Based on Low Power Consumption Technique

Kunal Geed<sup>1</sup>, Prof. Amit Thakur<sup>2</sup>

M. Tech. Scholar, Department of EC, SVCST, Bhopal, India<sup>1</sup>

Asst. Professor, Department of CSE, SVCST, Bhopal, India<sup>2</sup>

Abstract: Design implementation of SRAM cell based on low power consumption technique. In the field of VLSI research in electronic circuitry and memory is the basic demand of most electronic devices. RAM is used as main memory for small value devices that do not have a cache. Therefore, the construction of memory using an optimized SRAM cell in terms of process parameters, i.e. power consumption, quantity, area and delay, is a domain of VLSI research in electronic circuitry and memory. Critical analysis and the same are present circuit like 10T-SRAM in a functional way high power used but the SRAM-10T was found to have better performance in terms of speed but has a higher access time .These memory components are designed specifically using a CMOS transistor. They talk about CMOS power, the area and speed of each transistor is a big deal, but our proposed design knows are three types of design circuit things like LPCT-RD, LPCT-WD and LPCT. Engineers and researchers are still working on these questions. Various methods have been used to reduce power leakage within the designed circuit. As a circuit analysis processing, using memory capacity in design SRAM cell circuit is reduced power and also performance improves memory works like read, write and power saving better as compare existing circuit 10T. It is using simulation micro wind tool and also computing power, when compared to the results obtained in mode CMOS with micro wind tool. The 10T SRAM bit cell are not reduced power and performance not better the designed 10T SRAM bit cell showed in research study, poor performance, more power utilize of the 10T SRAM bit cell. Proposed design read times, write times access to LPCT-SRAM bit cell intended to increase and decrease volume but low power utilize and other side existing circuit 10T-SRAM model components are low performance. Finally our proposed circuits (LPCT) are reliable and efficient.

**Keywords**: VLSI, Memory, SRAM, DRAM, Power Consumption, Power Reduction, Power Dissipation, CMOS Technology, Read Delay, Write Delay LPCT.

### I. INTRODUCTION

SRAM (Random Access Memory) can also be a type of random semiconductor memory that uses latches or latches to store data, so that the data in its storage is permanent as long as its power is used. Another source of random access is DRAM (Random Random Access Memory), as well as MOS semiconductor memory, which uses a capacitor and a transistor to store data. SRAM and DRAM are memory modifiers. SRAM is more popular despite its high cost and low data collection compared to DRAM due to its speed i.e. cell data is often read at the speed of SRAM compared to DRAM. In addition, SRAM does not require occasional refresh like DRAM. Thus, SRAM can be an option for developers in applications where high speeds may be required, so the cost of the cell is as high as in the case of cache memory. In modern times when battery operated devices have become commonplace, blackouts and zones have become major causes of the need for smaller power generating devices. Every day, the size of the connection is increasing to satisfy the small number of small chips by small chips. This technological scale causes instability of SRAM cellular functions. Normal SRAM cartridges suffer from various low tech issues like leakage current, read stability, etc. to understand the design that can work on small technologies, different SRAM cells are developed. As there is a compromise between the different parameters of the SRAM cell, it is therefore not possible to realize all the components during the same design. Thus, different configurations according to different needs in many applications are optimized by considering 1 or more parameters. This article discusses the different types of SRAM cells that carry a unique number of transistors and have some advantages over smaller ones, so the advantages and disadvantages of different SRAM cells are different. RAM dominates most of the system on chip (SoC) and dominates system performance and control. Especially in bioelectronics and other emerging applications, low power and low SRAMs are required to expand the operating system with less power. Consequently, the design of low voltage and low power SRAM circuits [1] is constantly increasing. Two factors are important for the design of the SRAM cell: the surface area of the cell and therefore the stability of the cell. The two are interrelated since the design of the cell for optimum stability always requires the size of the cell area. As the device size continues to decrease, increasing current points, system changes, and random variations lead to errors. In addition, typing errors can occur due to the difficulty in maintaining the power value of the device in the ground area. The best way to improve SNM drive read is to remove cell storage nodes from the current read row, so that the SNM drive can contain

Vol. 10, Issue 12, December 2021

### DOI: 10.17148/IJARCCE.2021.101243

the SNM.To strengthen the WM and write operation, the maximum power is used to write the capacitance of transistor [2] and / or write the help circuits to the extra power and extra control value. Several SRAM cell systems that depend on soil function are presented in the literature. This article examines the latest types of SRAM models that address stability and reliability issues. The rest of the document is structured as follows. Section 2 reviews the different SRAM models. Section 3 includes the comments and section 4 concludes the article [1].

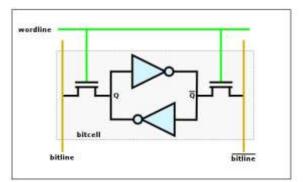

Fig.1 basic building block of SRAM memory

The SRAM bitcell is the real building block of SRAM memory. The cell keeps the same value as long as there is current. The two access points to the cell are called bit lines (BL). The bit lines contain the value of the stored bit and its precision. Two incoming transistors are on bit rows to enable and disable access to stored data for read and write activities. The signal that controls the input transistor is called the word line (WL).

### **II.LITERATURE REVIEW**

Various research activities have been carried out and are continuing every day to increase the reliability of the SRAM virus in order to overcome the trade-off between surface area, speed and power. A few of the research papers were reviewed and the activities carried out in the papers are listed below.

1) Mahendra Kumar and Kailash Chandra [4] suggest that data retention and leakage are now a major concern in today's CMOS technology. so get the higher noise side with the best performance new SRAM cartridges are introduced. In most cases, the work of reading and writing the cell is not put aside for additional noise. In large-size RAM memory chips, reduced performance is important to detect short-term, low-cost reliability, as it allows the temperature of the plastic. Thus, different circuit breaker technologies are developed based on the reduction of the load capacity, the working capacity and the current intensity. As a result, the working capacity of each generation is reduced despite the high output power, increased chip size and improved access. SRAM technology evolves towards high volume, high speed and low power. The maximum quantity and the best speed are obtained by scale. Reducing the actual oxide flow rate is important to understanding the high rate of hold time maintenance. Electricity consumption is reduced by reducing electricity supply and creating a navigation system. New technologies, such as Cu interconnects and small K 'dielectrics have been introduced for faster operation.

2) Simran Kaur and Ashwani Kumar [5] have suggested power failures during the process of writing to CMOS T CMOS SRAM six-T as well as reading. In its research work, the SRAM cell is shown in figure 11, it will include an additional transistor which can control the overall force during the writing and skimming process and improve the overall force resulting in reduced dissipation of the l'equipment. Here, during this project, they are targeting an electricity shortage, as the power supply is also called the power supply. The circuit is defined using 130nm technology which has q to generate a power of 1.5 volts and the grid power is 0.40 volts. The results were compared to a standard SRAM 6T cell which is also described in this review with the same technology. This small modified cell consumes less power, the average saves 54% compared to the SRAM cell.

3) VineshSrinivasan, VarshadVenkatraman.R, Senthilkumar.KK [3] suggest that the amount of power consumed during the operation of a regular SRAM 6T cell results in limited read and write capacity of the cell, thus causing confusion - confusion of the end. The Schmitt cell model solves this problem by providing an efficient response mechanism to adjust the correct switching of the inverter according to the input voltage. ST SRAM molecules have an efficient response mechanism to deal with variations in PVT, with the interaction with CNFET shown in Figure .10 providing unique electrical properties in the nanometer range, proving to be suitable for future cells. SRAM. When changing input node, the feedback transistor stores 1 at the output node by increasing the voltage source of NCNFET N1. This provides the best replacement for the inverter. During entry time, the entry response system refers to logic that provides the best transfer characteristics for the text function. The results transfer changing characteristics with respect to cell input and improve the read and write accuracy of SRAM cells

### Vol. 10, Issue 12, December 2021

### DOI: 10.17148/IJARCCE.2021.101243

4) Mo Maggie Zhang [1] suggests that the performance simulations of SRAM 6, 7 and 8T topologies are shown in Figures 1, 2 and 3. As process technology advances, the speed of SRAMs will increase. , but I Businesses grow. be very sensitive to jitter, which disturbs the direct noise (SNM) of SRAM cells. thanks to stress and stability, a two-port model that implements a stress-free read function like that seen in the 7T and 8T cell process might be most useful at the end of the SRAM cell implementation of the daytime. Although the 7T and 8T cell processes ended with a 13% and 30% increase respectively reported, these two topologies leave the best cell stability due to the unreadable function, which is useful as process technology is in decline.

5) Nakkala Suresh and Dr. VangalaPadmaja [2] strongly recommend Schmitt to design the SRAM source that is suitable for low power application applications in Figures 7 and 8. This response system is generally effective for nanoscale technology in the field. resistance, low performance of SRAM. The results of experimental simulations at Mentor Graphics EDA were analyzed with TSMC-250nm, TSMC-350nm technology. nanometric range, proving to be an ideal combination for future SRAM cells. When changing input node, the feedback transistor stores 1 at the output node by increasing the voltage source of NCNFET N1. This provides the best replacement for the inverter. During entry time, the entry response system refers to logic that provides the best transfer characteristics for the text function. The results transfer changing characteristics with respect to cell input and improve the read and write accuracy of SRAM cells.

6) Shilpi Birla1 and. al (2011) analyzed the 8T static random access memory cell at 65nm process technology is shown in Figure ..2. This topology was originally developed for high performance RAM and was developed to be more effective and efficient than the size of the power supply. The write process is carried out through the WWL, WBL and WBLX ports, while the single read function is implemented through the RWL and RBL ports. The RBL charges to the best of each read cycle and recharges during the write cycle. At this cell time, cell writing and thin port are separated as opposed to traditional 6T cell. The SNM reading problem has been eliminated and the vertical size of the 6T RAM is optimized for improved text without the RSNM trade. This causes the reduction of the inadequate readings to zero and therefore the inch on the reading line is drastically reduced. Vdd is that the virtual provides cross nodes with inverters and reduces its power when writing to weaken the PMOS loading device and alleviate the low voltage write problem. Because all of the bits, lines are written and skimmed correctly. Time, Vdd divides into parallel lines of memory cells.

7)proposes the fully differential low power 10T SRAM [10] bit cell is shown in Fig.5. The design strategy of cell is the series connection of tail transistor. The gate electrode of this device is controlled by the output of an XOR gate, inputs of which are tapped from write word line (WWL) and read word line (RWL) control signals coming from the WWL and the RWL drivers. The XOR gate and the tail transistor are shared by all the cells in a row. The tail transistor has to be appropriately up sized for sinking currents from all the cells in the row. Without this read buffer, a cell with such small drivers and series connected tail transistor would exhibit unacceptably low read static noise margin (RSNM), resulting in read instability.

### II. SIMULATION TOOL

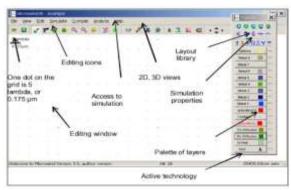

Microwind is genuinely incorporated EDA programming including IC plans from idea to culmination, empowering chip planners to plan past their creative mind. MICROWIND incorporates customarily isolated front-end and back-end chip plan into a coordinated stream, speeding up the plan cycle and decreased plan intricacies. It firmly incorporates inconsistent message execution with advanced execution, circuit reproduction, semiconductor level extraction and confirmation – giving imaginative schooling drive to assist people with fostering the abilities required for configuration positions in essentially every space of IC industry. Microwind instrument is genuinely coordinated Electronic plan robotization programming incorporating IC plans from idea to finish, empowering chip fashioners to plan past their creative mind. Microwind coordinates customarily isolated front-end and back-end chip plan into an incorporated stream, speeding up the plan cycle and diminishes plan intricacies. It firmly coordinates contradicting message execution with computerized execution, circuit reproduction, semiconductor level extraction, and check giving inventive schooling drive to assist people with fostering the abilities required for configuration positions in for all intents and purposes each space of IC industry. The MICROWIND programming permits the originator to recreate and plan a coordinated circuit at actual portrayal level. Microwind3 binds together schematic passage, design based test system, SPICE extraction of the schematic, Verilog extractor, format accumulation, on format blend signal circuit recreation, cross-sectional and 3D watcher, netlist extraction, BSIM4 instructional exercise on MOS gadgets and close down connection to convey unparalleled plan execution and fashioner efficiency. The bundle contains a library of normal rationale and simple ICs to see and recreate. Microwind3 incorporates every one of the orders for a cover proofreader also as, you can get sufficiently close to Circuit Simulation by squeezing only one single key. The electric extraction of your circuit is naturally performed and the simple test system produces voltage and flow bends quick. The apparatus includes full altering offices, different perspectives, and an on-line simple test system. The MICROWIND programming has following sections in show.

IJARCCE

Vol. 10, Issue 12, December 2021 DOI: 10.17148/IJARCCE.2021.101243

Fig2 The Microwind screen introduction stage format

### III. RESULT ANALYSIS

Microwind programming reenactments have been performed on microwind apparatus variant utilizing 90nm innovation with input voltage going up to 1V. To demonstrate that proposed plan shows better execution for read time compose time and power utilized, Microwind programming reproductions are completed for various voltages. To build up an unbiased testing climate the two circuits have been tried on similar information a design which covers all the blend of information stream. Proposed plan LPCT cells correlation 10T.

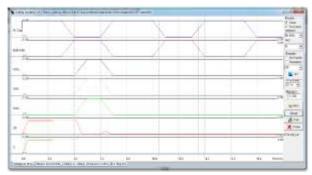

### (a) Read Delay Time based Power Use Analysis:

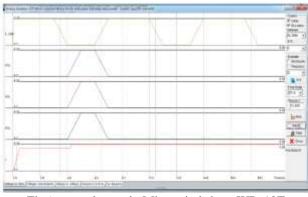

The Read-SRAM of the current RD-10T and the proposed RD-LPCT has been recreated for different Input voltages. The impact of Power Supply Voltage is significant boundary which changes the phone dependability during read mode and has been generally adequate. It is ideal that the stock voltage should be greatest for increment SRAM and furthermore for cell strength.

### 1. RD-10T:

Fig3 output layout in Microwind show RD-10T

For this investigation, the stockpile voltage is shifted from 0.4V to 1V. The clamor edge for all activity is relative to the stock voltage. The read-SRAM of the proposed RD-LPCT single piece SRAM Cell is higher than the current RD-10T single piece SRAM Cell as shown by the fig3 and fig4.

### 2. RD-LPCT:

Fig4 output layout in Microwind show RD-LPCT

© IJARCCE

# DARCE

### International Journal of Advanced Research in Computer and Communication Engineering

IJARCCE

Vol. 10, Issue 12, December 2021

DOI: 10.17148/IJARCCE.2021.101243

Power utilization versus Supply voltage of existing 10T and LPCT - RD SRAM Cell. Both outcome investigations in table1 shows below.

Table1. Power consumption vs. Supply voltage of existing 10T and LPCT -RD SRAM Cell.

| SRAM<br>Cells | Time Scale<br>(in ns) | Power<br>Consumption<br>(in uw) |

|---------------|-----------------------|---------------------------------|

| 10T           | 20                    | 74.407                          |

|               | 20                    | 8.747                           |

| LPCT -        |                       | 0.7.17                          |

| RD            | 20                    |                                 |

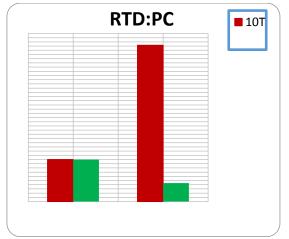

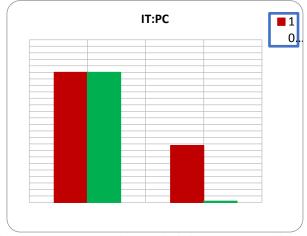

### 3. Power Consumption Analysis based on Read Delay Time (Result Graph):

The current 10T-RD and LPCT - RD have been reproduced and checked at different voltages for Power Consumption. Table 1 show that the power utilization of the proposed LPCT - RD Cell configuration increments with expanding supply voltage from 0.5V to 1V. The LPCT - RD plan of the SRAM Cell has strikingly less power utilization contrasted with the current 10T SRAM plan at different information voltages. Table 1 shows the variety of force utilization for existing and LPCT-RD memory plan. It is obvious from Table 1 that LPCT - RD memory configuration devours less power than existing 10T SRAM memory design.

Fig5 Power Consumption Analysis between 10T and LPCT -RD

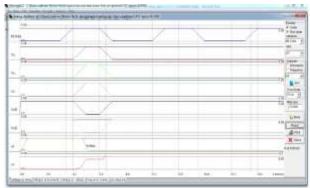

### (b) Write Delay Time based Power Use Analysis:

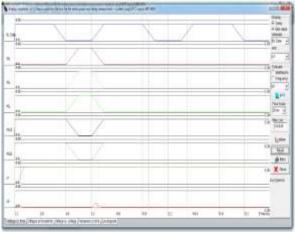

The Write - SRAM of the current WD-10T and the proposed WD-LPCT has been reproduced for different Input voltages. The impact of Power Supply Voltage is significant boundary which changes the phone steadiness during read mode and has been generally OK. It is ideal that the inventory voltage should be greatest for increment SRAM and furthermore for cell strength

1. WD-10T:

Fig6 output layout in Microwind show WD-10T

© IJARCCE This work is licensed under a Creative Commons Attribution 4.0 International License

226

# DARCE

### International Journal of Advanced Research in Computer and Communication Engineering

IJARCCE

Vol. 10, Issue 12, December 2021

### DOI: 10.17148/IJARCCE.2021.101243

For this investigation, the stockpile voltage is fluctuated from 0.4V to 1V. The commotion edge for all activity is relative to the inventory voltage. The read-SRAM of the proposed WD-LPCT single piece SRAM Cell is higher than the current WD-10T single piece SRAM Cell as shown by the fig6 and fig7. **2.WD-LPCT:**

Fig7 output layout in Microwind show WD-LPCT

Power utilization versus Supply voltage of existing 10T and LPCT - WD SRAM Cell. Both outcome investigation in table 2 shows below.

Table2. Power consumption vs. Supply voltage of existing 10T and LPCT -WD SRAM Cell.

| SRAM<br>Cells | Time<br>Scale(in<br>ns) | Power<br>Consumption<br>(in uw) |

|---------------|-------------------------|---------------------------------|

| 10T           | 20                      | 0.504                           |

| LPCT -WD      | 20                      | 0.296                           |

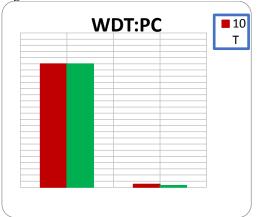

### 3. Power Consumption Analysis based on Write Delay Time (Result Graph):

The current 10T-WD and LPCT - WD have been reenacted and checked at different voltages for Power Consumption. Table2 show that the power utilization of the proposed LPCT - WD Cell configuration increments with expanding supply voltage from 0.5V to 1V. The LPCT - WD plan of the SRAM Cell has astoundingly less power utilization contrasted with the current 10T SRAM plan at different info voltages. Table2 shows the variety of force utilization for existing and LPCT-WD memory plan. It is obvious from Table 1that LPCT - WD memory configuration burns-through less power than existing 10T SRAM memory design.

Fig8 Power Consumption Analysis between 10T and LPCT -WD

### IJARCCE

### International Journal of Advanced Research in Computer and Communication Engineering

Vol. 10, Issue 12, December 2021

### DOI: 10.17148/IJARCCE.2021.101243

### (c)Power Use Analysis:

The current 10T and proposed LPCT have been reenacted and checked at different voltages for power use. Table3 show that the power utilization of SRAM Cell configuration increments with expanding supply voltage from 0.6V to 1V. The proposed LPCT plan of the SRAM Cell has strikingly less power utilization contrasted with the current 10T SRAM plan at different info voltages.

1.10T:

Fig9 output layout in Microwind show 10T

Table3 shows variety of force utilization for existing and proposed LPCT SRAM memory plan. It is obvious from Table3 that proposed LPCT SRAM memory configuration devours less power than existing 10T SRAM memory design.

### 2.LPCT:

Fig10 output layout in Microwind show LPCT

Power utilization versus Supply voltage of existing 10T and LPCT SRAM Cell. Both outcome examination in table3 shows below.

Table 3. Power consumption vs. Supply voltage of existing 10T and LPCT SRAM Cell.

| SRAM Cells | Time Scale (inns) | Power Consumption (in uw) |

|------------|-------------------|---------------------------|

| 10T        | 20                | 8.761mw                   |

| LPCT       | 20                | 0.199mw                   |

Vol. 10, Issue 12, December 2021

IJARCCE

DOI: 10.17148/IJARCCE.2021.101243

### **3.** Power Consumption Analysis based on ideal Time (Result Graph):

The current 10T and LPCT have been recreated and checked at different voltages for Power Consumption. Table 3 show that the power utilization of the proposed LPCT Cell configuration increments with expanding supply voltage from 0.5V to 1V

Fig11 Power Consumption Analysis between 10T and LPCT

The LPCT plan of the SRAM Cell has amazingly less power utilization contrasted with the current 10T SRAM plan at different info voltages. Table3 shows the variety of force utilization for existing and LPCT memory plan. It is obvious from Table 1that LPCT memory configuration burns-through less power than existing 10T SRAM memory design.

### V.CONCLUSION

Design implementation of SRAM cell based on low power consumption technique. The developed SRAM circuit on micro wind tools, 10T- SRAM cell has the more power use, more read delay and more write delay using 90nm CMOS technology. Variations in static RAM transistor topologies have been reviewed. Analysis with 8T and 10T-SRAM architecture. SRAM activities are studied in different buildings. Normal 10Ts have the lowest transistor values and make up the largest area. The standard 10T has the lowest transistor ratings and offers the same stability as the best zone. As the number of transistors increases, the SRAM area increases. The circuit voltage is increased to a voltage lower than upto1V compared to that of a standard SRAM 6T cell, but the surrounding PDP is significantly reduced at all voltages. While a significant reduction is seen in both lead time and power consumption compared to the SRAM 10T. The designed circle also has some flexibility to minimize the possibility of a weak point error. This article focuses on the design techniques used to construct SRAM cells. SRAM occupies the highest percentage in integrated circuits, which finds its application in high speed devices as well as in multi-port devices. Proposed design circuit low power consumption technique (LPCT) cells are compared from 10T-SRAM cell, both case power supply of one by one and performance analysis of WL and WLB, power reduction of the optimal solution is obtained for proposed low power consumption technique (LPCT) cell are reduced power consumption in write operation time and read operation time and finally our proposed circuits (LPCT) are reliable and efficient.

#### REFERENCES

- Kumar, Mahendra, and Kailash Chandra. "Low Power High Performance SRAM Design Using VHDL." Global Journal of Research In Engineering 11, no. 1,2011.

- [2] Simran Kaur, Ashwani Kumar Analysis of Low Power SRAM Memory Cell using Tanner Tool," International Journal of Electronics & Communication Technology Volume. 3, Issue 1, Jan - March 2012.

- [3] Vinesh Srinivasan ,Varshad Venkatraman.R, Senthil kumar.K.K —Schmitt Trigger Based SRAM Cell for Ultralow Power Operation-A CNFET Based Approachl International Conference On design and manufacturing, IConDM 2013. Published by Science Direct Procedia Engineering 64 ( 2013) 115 – 124.

- [4] Mo Maggie Zhang, —Performance Comparison of SRAM Cells Implemented in 6, 7 and 8-Transistor Cell Topologiesl, Electrical and Computer Engineering, University of California, Davis

- [5] Nakkala Suresh, Dr Vangala Padmaja, JLV Ramana Kumari Low Voltage Low Power SRAM design based on Schmitt Trigger techniquel, IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 3, Issue 5 (Nov. – Dec. 2013), PP 01-06

- [6] Shilpi Birla1, Neeraj Kumar Shukla, KapilRathi, Rakesh Kumar Singh, ManishaPattanaik,"Analysis of 8T SRAM Cell at Various Process Corners at 65 nm Process Technology," Circuits and Systems, pp.326-329, 2011.

- [7] Singh S, Arora N, Gupta N, Suthar M. Leakage reduction in differential I0T SRAM cell using gated VDD control technique. In: International conference on computing, electronics and electrical technologies, p. 610–4, 2012

- [8] M. Nobakht and R. Niaraki, "A new 7T SRAM cell in sub-threshold region with a high performance and small area with bit interleaving capability," in IET Circuits, Devices & Systems, vol. 13, no. 6, pp. 873-878, 9 2019.

### IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering

### Vol. 10, Issue 12, December 2021

#### DOI: 10.17148/IJARCCE.2021.101243

- [9] G. Prasad, and Alekhya Anand, "Statistical analysis of low power SRAM cell structure", Analog Integrated Circuits and Signal Processing, 2015.

- [10] S. Naghizadeh and M. Gholami, "Two Novel Ultra-Low-Power SRAM Cells with Separate Read and Write Path," Circuits, Systems, and Signal Processing, springer, 38, no. 1, 2019.

- [11] H. Fujiwara et al., "A 64-Kb 0.37V 28nm 10T-SRAM with mixed- Vth read-port and boosted WL scheme for IoT applications," IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, 2016.

- [12] S. Keshavarapu, S. Jain and M. Pattanaik, "A New Assist Technique to Enhance the Read and Write Margins of Low Voltage SRAM Cell," International Symposium on Electronic System Design (ISED), Kolkata, pp. 97-101, 2012.

- [13] J. K. Mishra, H. Srivastava, P. K. Misra and M. Goswami, "Analytical modelling and design of 9T SRAM cell with leakage control technique", Analog Integrated Circuits and Signal Processing, 2019.

- [14] HareKrishnaKumar, V.K.Tomar " Single Bit 7T Sub-threshold SRAM cell for Ultra Low Power applications," International Journal of Advanced Science and Technology, Vol. 28, No. 16, (2019), pp. 345-351

- [15] Palagiri, H. V., Makkena, M. L., & Chantigari, K. R. (2013b). Optimum decimation and filtering for reconfigurable sigma delta adc. Far East Journal of Electronics and Communications, 11(2), 101–111.

- [16] P. Sandeep, P. A. Harsha Vardhini and V. Prakasam, "SRAM Utilization and Power Consumption Analysis for Low Power Applications," 2020 International Conference on Recent Trends on Electronics, Information, Communication & Technology (RTEICT), Bangalore, India, 2020, pp. 227-231.

- [17] Achiranshu Garg and Tony Tae-Hyoung Kim, "SRAM Array Structures for Energy Efficiency Enhancement, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS— II: EXPRESS BRIEFS, VOL. 60, NO. 6, pp. 351-355, JUNE 2013.

- [18] Praveen Elakkumanan, Charan Thondapu and Ramalingam Sridhar "DG-SRAM: A Low Leakage Memory Circuit" in Low Power Memory IEEE Conf., pp. 167-170, 2005

- [19] Cody Mitchell, Crystal L. McCartney, Mitchell Hunt & Fat D. Ho, "Characteristics of a Three-Transistor DRAM Circuit Utilizing a Ferroelectric Transistor." Integrated Ferroelectrics, vol. 157, no. 1, pp. 31-38, Jun 2014

- [20] Komal J. Anasane, Ujwala A. Kshirsagar, "A Review on Memristor MOS Content Addressable Memory (MCAM) Design Using 22nm VLSI Technology," International Journal of Scientific and Research Publications, vol. 5, no. 3, pp. 1-4, March 2015