International Journal of Advanced Research in Computer and Communication Engineering

# Design and Verification of low noise and low power amplifier

### Pramod M<sup>1</sup>, Prasanna N H<sup>2</sup>, Rohan N V<sup>3</sup>, Tanush R<sup>4</sup>, Mrs. Shilpa V<sup>5</sup>

Student, Electronics and Communication Engineering, SJB Institute of Technology, Bengaluru, India<sup>1-4</sup>

Assistant Professor, Electronics and Communication Engineering, SJB Institute of Technology, Bengaluru, India<sup>5</sup>

**Abstract**: This research presents the design and verification of a low-noise, low-power amplifier (LNA) optimized for high-performance applications such as wireless communication, IoT devices, and medical sensors. The design is implemented using 45nm CMOS technology in Cadence Virtuoso to achieve an optimal balance between noise figure, power efficiency, gain, and bandwidth. The proposed LNA incorporates inductive degeneration, resistive feedback, and cascading topologies to minimize thermal noise and enhance gain. The design undergoes extensive DC, AC, noise, transient, and Monte Carlo simulations to validate robustness. Post-layout verifications, including Design Rule Check (DRC) and Layout vs. Schematic (LVS), ensure fabrication compliance. The results demonstrate a power consumption of 22.4mW, making this design suitable for energy-efficient high-frequency applications.

Keywords: Low noise and Low Power Amplifier, 45nm CMOS Technology.

#### I. INTRODUCTION

The demand for low-noise and low-power amplifiers (LNAs) has grown significantly with the advancement of modern communication systems, medical devices, and sensor networks. LNAs are critical in amplifying weak input signals while minimizing added noise, thereby ensuring high signal fidelity and system performance. Applications such as wireless communication, satellite systems, radar, and IoT devices rely heavily on LNAs to function efficiently under stringent power and noise constraints.

Designing an LNA presents unique challenges due to the inherent trade-offs between noise figure, power consumption, linearity, and bandwidth. Achieving low noise levels often requires increased power consumption, making the design of an energy-efficient LNA a complex optimization problem. Furthermore, with the integration of LNAs into portable devices, reducing power consumption without compromising performance has become a primary objective for researchers and engineers.

This project aims to design and verify a high-performance LNA that operates with low power consumption while maintaining a low noise figure. The design process incorporates advanced CMOS technology to achieve optimal performance in terms of gain, input-output matching, and linearity. Verification of the design is carried out using simulation tools and post-layout analysis to ensure it meets industry standards.

#### Challenges in LNA Design

Designing an energy-efficient, low-noise amplifier presents several challenges:

- Noise Reduction: Achieving a low Noise Figure (NF) while maintaining high gain and bandwidth.

- Power Efficiency: Reducing power consumption to enhance battery life in portable and IoT devices.

- Impedance Matching: Ensuring input-output matching to minimize signal reflections and maximize power transfer.

- Process Variations: Addressing parasitic effects and layout-dependent effects (LDEs) in 45nm CMOS technology.

#### **Objective of This Research**

This research aims to:

- Design an LNA using 45nm CMOS that achieves an optimal trade-off between noise and power efficiency.

- Use advanced CMOS techniques such as inductive degeneration and resistive feedback to enhance gain and reduce power consumption.

##

#### International Journal of Advanced Research in Computer and Communication Engineering

IJARCCE

Impact Factor 8.102  $\,\,st\,$  Peer-reviewed / Refereed journal  $\,\,st\,$  Vol. 14, Issue x, Month 2025

### DOI: 10.17148/IJARCCE.2025.14xx

• Validate the robustness and reliability of the design using Monte Carlo and corner analysis simulations.

#### II. COMPARISON BETWEEN DIFFERENT TECHNOLOGIES [1][2][3][5]

| SL  | Study                  | Technology    | Topology     | Key Focus           | Limitations           |

|-----|------------------------|---------------|--------------|---------------------|-----------------------|

| No. |                        |               |              |                     |                       |

| 1   | Sharma et al. (2024)   | 45nm CMOS     | Inductive    | Low Noise Figure,   | No Feedback           |

|     | "Design of CMOS        |               | Degeneration | High Linearity      | Implementation for    |

|     | Low Noise Amplifier    |               | LNA          |                     | Stability             |

|     | with Inductive         |               |              |                     |                       |

|     | Degeneration for       |               |              |                     |                       |

|     | Navigation             |               |              |                     |                       |

|     | Application"[1]        |               |              |                     |                       |

| 2   | Sankaran &             | Not Specified | Adaptive     | Dynamic Biasing for | No Fixed Trade-off    |

|     | Purushothaman          |               | Biasing LNA  | Performance Tuning  | Optimization          |

|     | (2023) "Adaptive       |               |              |                     |                       |

|     | Enhancement of Low     |               |              |                     |                       |

|     | Noise Amplifier        |               |              |                     |                       |

|     | Using Cadence          |               |              |                     |                       |

|     | Virtuoso Tool"[2]      |               |              |                     |                       |

| 3   | Chrisvin et al. (2022) | 90nm CMOS     | Common       | High Gain, Low      | Stability Challenges, |

|     | "Design and Study of   |               | Source LNA   | Flicker Noise.      | Higher Power          |

|     | 90nm CMOS              |               |              |                     | Consumption           |

|     | Common Source          |               |              |                     |                       |

|     | 2.4GHz Low Noise       |               |              |                     |                       |

|     | Amplifier"[3]          |               |              |                     |                       |

| 4   | Abhay Chaturvedi,      | 180nm CMOS    | Ultra-       | Demonstrated        | Higher Power          |

|     | Manish Kumar &         |               | Wideband     | Viability of 180nm  | Consumption           |

|     | Neelam Gautam          |               | LNA          | CMOS for UWB        | Compared to           |

|     | (2015) "Design and     |               |              | Applications        | Advanced Nodes        |

|     | Implementation of      |               |              |                     |                       |

|     | Low-Noise Amplifier    |               |              |                     |                       |

|     | for Ultra-Wideband     |               |              |                     |                       |

|     | Receiver in 180nm      |               |              |                     |                       |

|     | CMOS                   |               |              |                     |                       |

|     | Technology"[5]         |               |              |                     |                       |

### IJARCCE

#### International Journal of Advanced Research in Computer and Communication Engineering

#### DOI: 10.17148/IJARCCE.2025.14xx

#### III. PROPOSED METHODOLOGY

#### **Technology Selection**

- Fabrication node: 45nm CMOS

- Tool: Cadence Virtuoso

- **Operating Frequency:** GHz-range (targeting 5G and IoT applications)

#### LNA Topologies Explored

- Common Gate LNA Offers wideband input matching but suffers from moderate noise performance. 1.

- 2. **Common Source LNA** – Provides high gain but requires careful impedance matching.

- 3. Resistive Parallel Feedback LNA - Achieves good stability and bandwidth, though with increased noise due to feedback resistance.

- Cascading Resistive Parallel LNA Extends bandwidth while maintaining a low noise figure. 4.

#### **Proposed LNA Design**

- Combines inductive degeneration and resistive feedback to achieve low noise and efficient power consumption. .

- Optimized transistor sizing to balance gain and bandwidth trade-offs.

- Biasing circuits optimized for low power consumption.

- Post-layout optimization to mitigate parasitic effects.

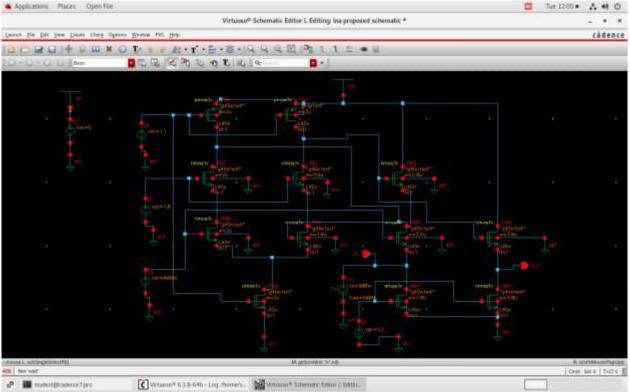

#### Figure 1- Proposed design of LNA

#### **IV.SIMULATION AND RESULTS**

The designed LNA was validated using Cadence Virtuoso Spectre simulator through multiple analyses: 1. DC Analysis

Bias stability confirmed, ensuring reliable transistor operation.

#### International Journal of Advanced Research in Computer and Communication Engineering

Impact Factor 8.102  $\,\,symp \,$  Peer-reviewed / Refereed journal  $\,\,symp \,$  Vol. 14, Issue x, Month 2025

#### DOI: 10.17148/IJARCCE.2025.14xx

#### 2. AC Analysis

NМ

- Gain: 18 dB

- Bandwidth: Sufficient for GHz-range applications

#### 3. Noise Analysis

• Noise figure (NF): Optimized below 2 dB, making it highly suitable for high-sensitivity applications.

#### 4. Power Consumption

- Common Source LNA: 107.3mW

- Resistive Feedback LNA: 81.5mW

- Cascading LNA: 77.4mW

- Proposed LNA: 22.4mW  $\rightarrow$  Significant reduction compared to previous designs.

#### 5. Monte Carlo and Corner Analysis

- Ensured robustness under process variations.

- Stability across temperature and voltage changes.

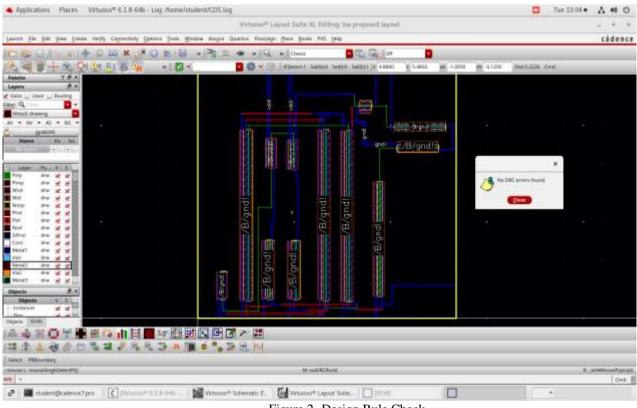

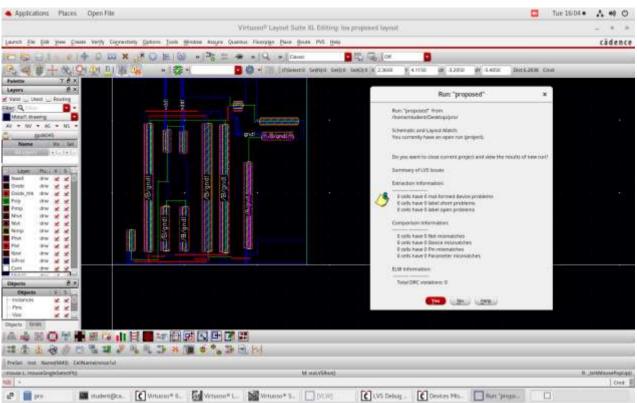

#### 6. Layout Design and Post-Layout Verification

- DRC (Design Rule Check): Passed with no violations.

- LVS (Layout vs. Schematic): Verified correct implementation.

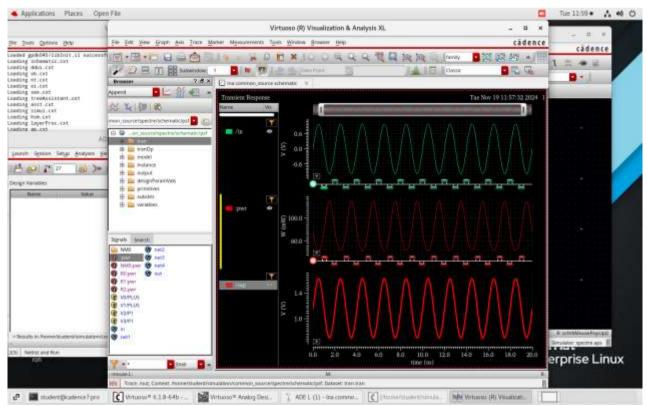

- Parasitic extraction performed, showing minimal deviation from pre-layout simulations.

Figure 2- Design Rule Check

### IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering Impact Factor 8.102 ∺ Peer-reviewed / Refereed journal ∺ Vol. 14, Issue x, Month 2025 DOI: 10.17148/IJARCCE.2025.14xx

Figure 3- Layout vs Schematic check

Figure 4- Transient analysis after parasitic extraction.

### IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering

Impact Factor 8.102  $~\cong~$  Peer-reviewed / Refereed journal  $~\cong~$  Vol. 14, Issue x, Month 2025

DOI: 10.17148/IJARCCE.2025.14xx

#### V. CONCLUSION AND FUTURE WORK

#### **Key Findings**

NΜ

- Low noise figure (~2 dB) with high gain (~18 dB).

- Significant power reduction (22.4mW), making it ideal for portable applications.

- Validated stability across process variations using Monte Carlo simulations.

- Successfully verified layout with no DRC/LVS errors.

#### **Future Work**

- Implementing the design in more advanced CMOS nodes (e.g., 22nm, 16nm).

- Fabrication and real-world testing to validate simulated results.

- Exploring machine learning techniques for further optimization.

#### REFERENCES

- Sharma, Abhishek & Kalra, Dheeraj & Kumar, Manish & Bhatia, Rajiv. (2024). Design of CMOS low noise amplifier with inductive degeneration for navigation application. Journal of Electrical Engineering, doi: 75.458-466.10.2478/jee-2024-0054.

- [2]. K. S. Sankaran and K. E. Purushothaman, "Adaptive Enhancement of Low Noise Amplifier Using Cadence Virtuoso Tool," 2023 Second International Conference on Recent Trends and Challenges in Computational Models (ICRTCCM), Tindivanam, India, 2023, pp. 330-334, doi: 10.1109/ICRTCCM.2023.37.

- [3]. D. Sam Chrisvin, M. Dharshini, S. N. Senthilkumar and T. Jaspar Vinitha Sundari, "Design and Study of 90nm CMOS Common Source 2.4GHz Low Noise Amplifier," 2022 6th International Conference on Computing Methodologies and Communication (ICCMC), Erode, India, 2022, pp. 545-550, doi:10.1109/ICCMC53470.2022.9753775.

- [4]. Anjana Jyothi Banu, G. Kavya, D. Jahnavi, Performance Analysis of CMOS Low Noise Amplifier Using ADS and Cadence, Materials Today: Proceedings, Volume 24, Part 3, 2020, Pages 1981-1986, ISSN 2214-7853, https://doi.org/10.1016/j.matpr.2020.03.626.

- [5]. Gautam, Neelam & Kumar, Manish & Chaturvedi, Abhay. (2015). DESIGN AND IMPLEMENTATION OF LOW-NOISE AMPLIFIER FOR ULTRA-WIDEBAND RECEIVER IN 180nm CMOS TECHNOLOGY. ICTACT Journal on Microelectronics. doi: 01.68-71.10.21917/ijme.2015.0012.

- [6]. P. Heydari, "Design and Analysis of a Performance-Optimized CMOS UWB Distributed LNA," in IEEE Journal of Solid-State Circuits, vol. 42, no. 9, pp. 1892-1905, Sept. 2023, doi: 10.1109/JSSC.2007.903046.

- [7]. K. E. Purushothaman and V. Nagarajan, "Designing an low noise amplifier with high bandwidth & low power consumption," 2016 International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 2016, doi:10.1109/ICCSP.2016.7754113.

- [8]. J. -H. Kim, J. -T. Son, J. -T. Lim, H. -W. Choi and C. -Y. Kim, "Ultralow Noise Figure and Broadband CMOS LNA With Three-Winding Transformer and Large Transistor," in IEEE Transactions on Microwave Theory and Techniques, vol. 72, no. 5, pp. 2734-2744, May 2024, doi: 10.1109/TMTT.2024.3354908.

- [9]. Mahmou Raja & Faitah, Khalid. (2024). Design of a Low Power Low-Noise Amplifier with Improved Gain/Noise Ratio. World Journal of Engineering and Technology. 12. 80-91. 10.4236/wjet.2024.121005.

- [10]. Galante-Sempere D, del Pino J, Khemchandani SL, García-Vázquez H. Miniature Wide-Band Noise-Canceling CMOS LNA. Sensors. 2022; 22(14):5246. https://doi.org/10.3390/s22145246.