# “OPTIMIZED VLSI DESIGN FOR REAL-TIME EDGE DETECTION”

**Dr. S G Hiremath<sup>1</sup>, Sudeep S B<sup>2</sup>, Akash Gowda K S<sup>3</sup>, Siddesh D S<sup>4</sup>, Vikas H M<sup>5</sup>**

Head of the Department, ECE, East West Institute of Technology, Bangalore, India<sup>1</sup>

Student, ECE, East West Institute of Technology, Bangalore, India<sup>2</sup>

Student, ECE, East West Institute of Technology, Bangalore, India<sup>3</sup>

Student, ECE, East West Institute of Technology, Bangalore, India<sup>4</sup>

Student, ECE, East West Institute of Technology, Bangalore, India<sup>5</sup>

**Abstract:** Edge detection is a foundational operation in computer vision and embedded image processing, enabling systems to identify structural boundaries and salient features within visual data. Real-time implementation of edge detection remains challenging in software platforms due to high computational load and latency. To address this limitation, a hardware-optimized VLSI architecture implementing the Sobel operator is proposed for real-time video edge extraction. The system acquires live frames through a VGA camera, performs grayscale conversion, calculates horizontal and vertical gradients using Sobel convolution masks, and computes edge magnitude before applying thresholding. Implemented on the Artix-7 FPGA using Verilog HDL, the design leverages parallelism, pipelining, on-chip memory optimization, and low-power computation. Experimental evaluation demonstrates significant improvements in throughput, latency, and resource efficiency over traditional software-based methods. The architecture is suitable for embedded vision applications such as surveillance, robotics, and smart IoT cameras.

**Keywords:** Sobel, VLSI, FPGA, Edge Detection, Verilog, Real-Time Video Processing.

## I. INTRODUCTION

Edge detection aims to identify sharp intensity changes in an image, which signify meaningful transitions such as object boundaries, shape contours, and texture variations. It represents a crucial preprocessing step in high-level vision tasks including segmentation, recognition, autonomous navigation, and motion tracking. Classical algorithms such as Sobel, Prewitt, Roberts, Scharr, and Canny have been widely used for edge extraction. However, deploying these methods on CPUs or microcontrollers leads to significant processing delays, especially for video streams.

Field-Programmable Gate Arrays (FPGAs) offer a promising alternative by providing parallel computation, configurable logic, pipelines, and low-power operation, making them ideal for real-time image processing. The Sobel operator, due to its simple mask-based arithmetic and robustness to minor noise, is highly suitable for FPGA-based implementation. This work presents a complete VLSI architecture for real-time Sobel edge detection. The system comprises live video acquisition using a VGA camera, grayscale conversion, Sobel gradient computation ( $G_x, G_y$ ), magnitude calculation, thresholding, buffering, and VGA-based display. All modules are designed in Verilog HDL and synthesized on an Artix-7 FPGA platform. This ensures fast, deterministic, and energy-efficient edge extraction suitable for embedded video applications.

## II. METHODOLOGY

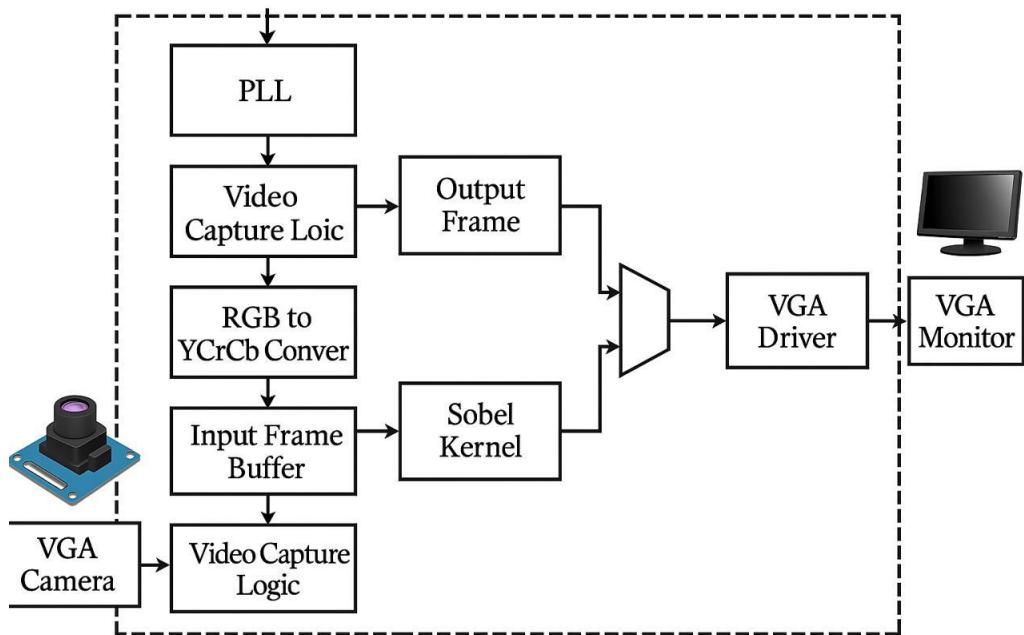

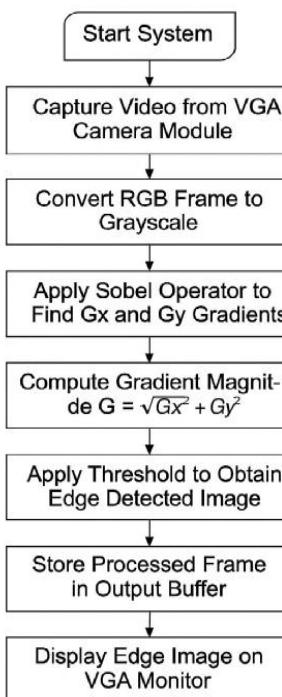

The proposed system follows a systematic hardware-centric methodology for achieving real-time video edge detection on an FPGA platform. Live video frames are first captured using a VGA camera module, which streams pixel data to the FPGA in RGB format. Since direct processing of RGB components increases computational complexity, the frames are immediately converted into grayscale using a hardware-efficient weighted approximation, thereby reducing the data width and simplifying subsequent operations. To enable  $3 \times 3$  neighborhood processing required for Sobel convolution, the incoming grayscale pixel stream is passed through line buffers implemented using on-chip BRAM, which generate three parallel rows of pixels forming a sliding  $3 \times 3$  window. This window is fed into two parallel Sobel convolution units that compute the horizontal ( $G_x$ ) and vertical ( $G_y$ ) gradients using shift-and-add operations instead of multipliers, improving speed and reducing resource usage. The gradient values are then combined using a hardware-friendly magnitude approximation  $|G_x| + |G_y|$  that avoids complex square-root calculations. A programmable threshold module

converts the gradient magnitude into a binary edge map by classifying strong gradient transitions as edges. The processed edge pixels are stored temporarily in an output buffer to ensure synchronization with the VGA display controller. Finally, the FPGA generates appropriate HSYNC, VSYNC, and pixel clock signals to display the edge-detected video frames on a VGA monitor in real time. The entire architecture is designed using Verilog HDL, synthesized and implemented in Xilinx Vivado, utilizing a pipelined and parallelized design approach that ensures low latency, high throughput, and efficient FPGA resource utilization.

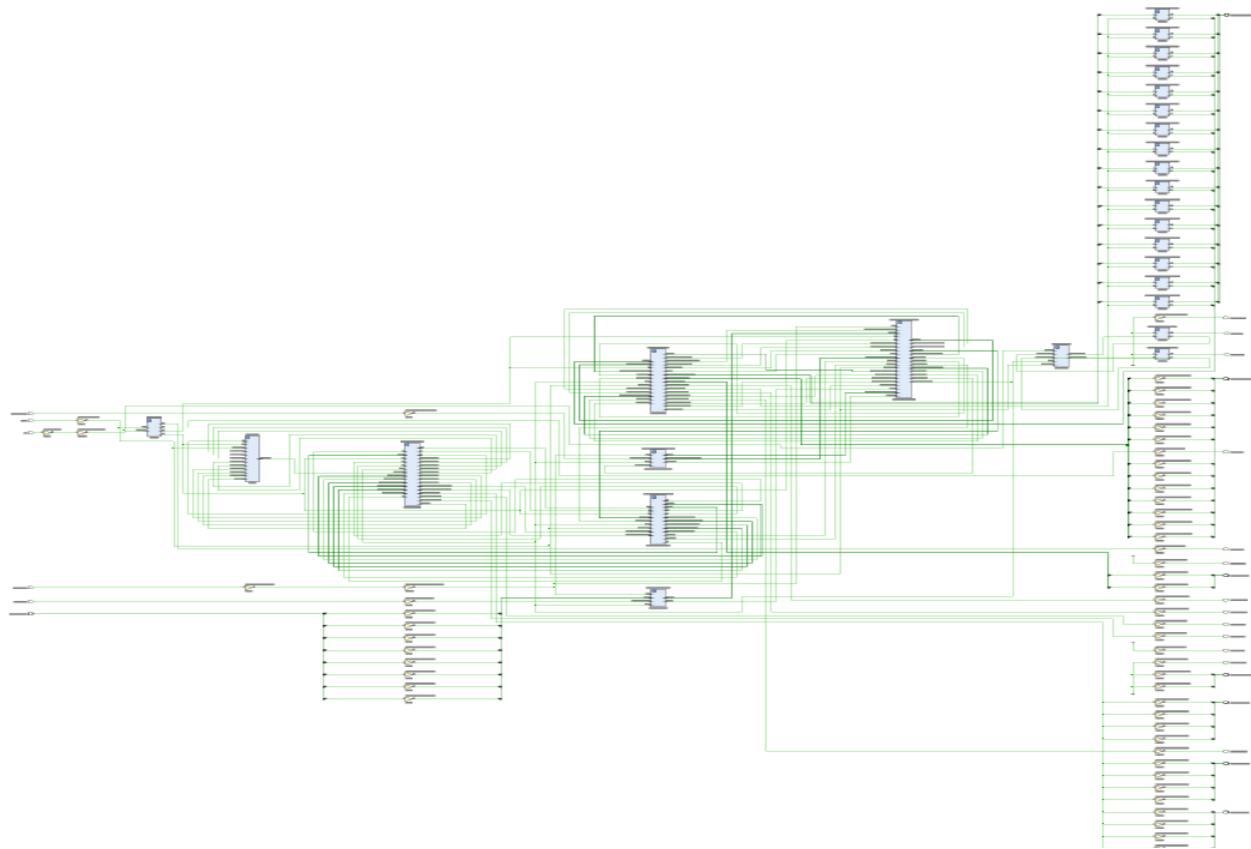

Figure 1: System Architecture

### III. IMPLEMENTATION

Figure 2: Implementation Steps.

## RESULT

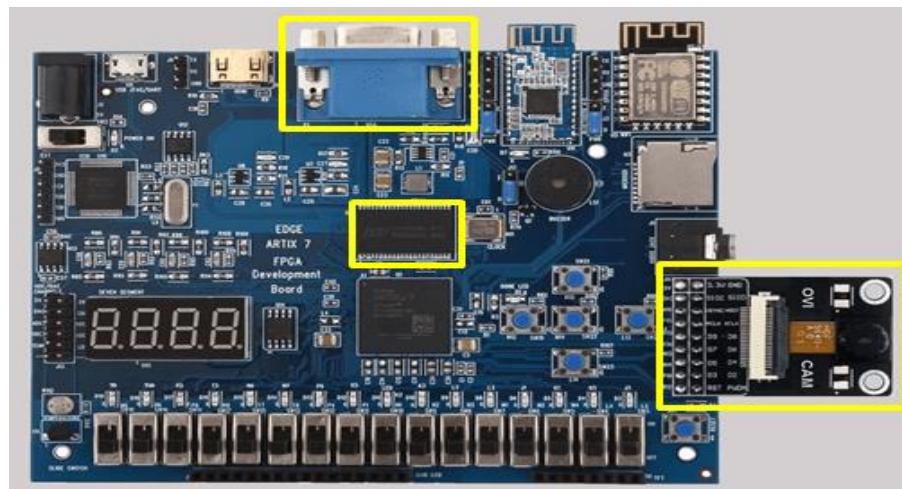

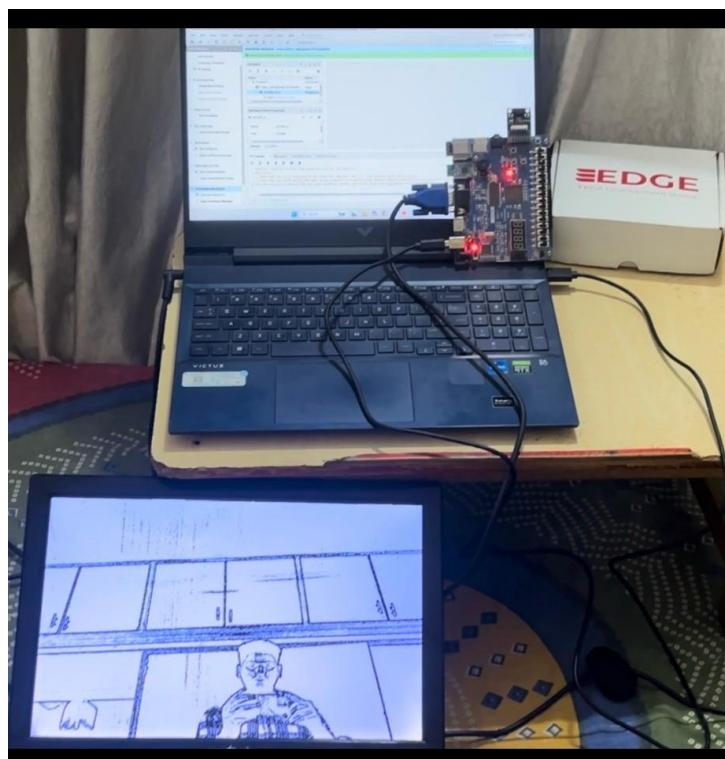

Fig: Artix 7 FPGA Board.

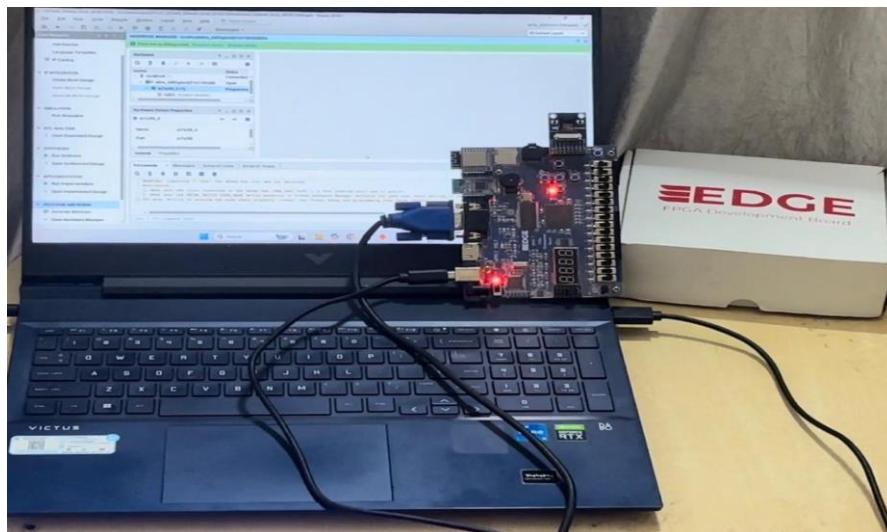

Fig: Experimental Setup

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 1109        | 20800     | 5.33          |

| LUTRAM   | 3           | 9600      | 0.03          |

| FF       | 952         | 41600     | 2.29          |

| BRAM     | 2.50        | 50        | 5.00          |

| IO       | 71          | 170       | 41.76         |

| BUFG     | 7           | 32        | 21.88         |

| MMCM     | 1           | 5         | 20.00         |

Fig: FPGA Post Synthesis Results

Fig: RTL Schematic of top level module.

Fig: Sample Output

**IV. CONCLUSION**

This work demonstrates a fully developed VLSI architecture for real-time video edge detection using the Sobel operator. The implementation on the Artix-7 FPGA validates the proposed design's efficiency in terms of speed, accuracy, and resource usage. By combining parallelism, pipelining, and optimized memory structures, the system achieves high-performance edge detection suitable for embedded vision. Future work may involve optimizing noise resistance using Gaussian smoothing or expanding the pipeline to include advanced edge detectors.

**ACKNOWLEDGMENT**

I would like to express my heartfelt gratitude to everyone who has supported, guided, and encouraged me throughout the duration of this project.

First and foremost, I extend my sincere thanks to my project guide and faculty members for their valuable advice, continuous assistance, and unwavering support. Their expertise, motivation, and constructive feedback played a crucial role in the successful completion of this work.

I am also deeply thankful to the laboratory staff and technical team for their help with hardware configuration, debugging, and system integration. Their cooperation, timely suggestions, and hands-on assistance were instrumental in overcoming various challenges encountered during the development phase.

A heartfelt appreciation goes to my family and friends for their constant encouragement, patience, and belief in me. Their support kept me motivated and focused throughout the entire project journey.

Lastly, I express my gratitude to the institution for providing the necessary facilities, resources, and learning environment, as well as to various online platforms that enhanced my understanding and contributed significantly to the completion of this project.

This project would not have been possible without the collective support of all these individuals, and I am genuinely thankful for their contributions.

**REFERENCES**

- [1]. J. Balcerk, A. Konieczka, T. Marciniak, A. Dąbrowski, K. Maćkowiak, and K. Piniarski, "Video processing approach for supporting pedestrians in vehicle detection," in Proceedings of the 2014 Signal Processing: Algorithms, Architectures, Arrangements, and Applications (SPA), Poznan, Poland, pp. 100-103, 2014.

- [2]. V. Boyun, "Directions of development of intelligent real-time video systems," in Proceedings of the 2016 International Conference Radio Electronics & Info Communications (UkrMiCo), Kiev, Ukraine, pp. 1- 7, 2016. <https://doi.org/10.1109/UkrMiCo.2016.7739640>.

- [3]. P. R. P. Tammana and B. Penumutchi, "An Exploration on Competent Video Processing Architectures," in Proceedings of the 2023 International Conference for Advancement in Technology (ICONAT), Goa, India, pp. 1-6, 2023. <https://doi.org/10.1109/ICONAT57137.2023.10080628>.

- [4]. M. Mittal et al., "An Efficient Edge Detection Approach to Provide Better Edge Connectivity for Image Analysis," IEEE Access, vol. 7, pp. 33240-33255, 2019. <https://doi.org/10.1109/ACCESS.2019.2902579>.

- [5]. N. Prakash, S. Asif Basha, S. Chowdhury, B. Reshma, D. Kapila, and S. Devi, "Implementation of Image Segmentation with Prewitt Edge Detection using VLSI Technique," in Proceedings of the 2022 International Conference on Innovative Computing, Intelligent Communication and Smart Electrical Systems (ICSES), Chennai, India, pp. 1-6, 2022. <https://doi.org/10.1109/ICSES55317.2022.9914259>.

- [6]. A. H. Ballado et al., "Philippine currency paper bill counterfeit detection through image processing using Canny Edge Technology," in Proceedings of the 2015 International Conference on Humanoid, Nanotechnology, Information Technology, Communication and Control, Environment and Management (HNICEM), Cebu, Philippines, pp. 1-4, 2015. <https://doi.org/10.1109/HNICEM.2015.7393184>.

- [7]. A. Asaduzzaman, A. Martinez, and A. Sepehri, "A time-efficient image processing algorithm for multicore/manycore parallel computing," in Proceedings of the SoutheastCon 2015, Fort Lauderdale, FL, USA, pp. 1-5, 2015. <https://doi.org/10.1109/SECON.2015.7132924>.